A000003 Arduino, A000003 Datasheet - Page 161

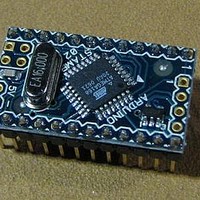

A000003

Manufacturer Part Number

A000003

Description

MCU, MPU & DSP Development Tools MINI

Manufacturer

Arduino

Series

-r

Type

MCUr

Specifications of A000003

Processor To Be Evaluated

Atmega328

Processor Series

ATmega

Data Bus Width

8 bit

Interface Type

USB, RS-232

Operating Supply Voltage

7 V to 9 V

Contents

Board

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

For Use With/related Products

ATmega168

- Current page: 161 of 378

- Download datasheet (8Mb)

ATmega48/88/168

(1)

Figure 18-1. SPI Block Diagram

DIVIDER

/2/4/8/16/32/64/128

Note:

1. Refer to

Figure 1-1 on page

2, and

Table 13-3 on page 77

for SPI pin placement.

The interconnection between Master and Slave CPUs with SPI is shown in

Figure

18-2. The sys-

tem consists of two shift Registers, and a Master clock generator. The SPI Master initiates the

communication cycle when pulling low the Slave Select SS pin of the desired Slave. Master and

Slave prepare the data to be sent in their respective shift Registers, and the Master generates

the required clock pulses on the SCK line to interchange data. Data is always shifted from Mas-

ter to Slave on the Master Out – Slave In, MOSI, line, and from Slave to Master on the Master In

– Slave Out, MISO, line. After each data packet, the Master will synchronize the Slave by pulling

high the Slave Select, SS, line.

When configured as a Master, the SPI interface has no automatic control of the SS line. This

must be handled by user software before communication can start. When this is done, writing a

byte to the SPI Data Register starts the SPI clock generator, and the hardware shifts the eight

bits into the Slave. After shifting one byte, the SPI clock generator stops, setting the end of

Transmission Flag (SPIF). If the SPI Interrupt Enable bit (SPIE) in the SPCR Register is set, an

interrupt is requested. The Master may continue to shift the next byte by writing it into SPDR, or

signal the end of packet by pulling high the Slave Select, SS line. The last incoming byte will be

kept in the Buffer Register for later use.

When configured as a Slave, the SPI interface will remain sleeping with MISO tri-stated as long

as the SS pin is driven high. In this state, software may update the contents of the SPI Data

Register, SPDR, but the data will not be shifted out by incoming clock pulses on the SCK pin

until the SS pin is driven low. As one byte has been completely shifted, the end of Transmission

161

2545S–AVR–07/10

Related parts for A000003

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO UNO PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO SHIELD PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO KIT REV 3

Manufacturer:

Arduino

Part Number:

Description:

Daughter Cards & OEM Boards ARDUINO MEGA PROTO PCB REV 3

Manufacturer:

Arduino

Part Number:

Description:

Development Boards & Kits - AVR ARDUINO STARTER KIT W/ UNO REV3

Manufacturer:

Arduino

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS PROTO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

RF Development Tools ARDUINO SHIELD WIRELESS WITH SD

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Development Software Getting started w/Arduino

Manufacturer:

Arduino

Part Number:

Description:

Ethernet Modules & Development Tools Ethernet Shield for Arduino

Manufacturer:

Arduino

Part Number:

Description:

MCU, MPU & DSP Development Tools LilyPad Arduino Main Board

Manufacturer:

Arduino

Part Number:

Description:

ARDUINO NANO Board

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Ethernet Modules & Development Tools ETHERNET SHEILD PoE FOR ARDUINO

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

ATMEGA328 MCU IC W/ Arduino UNO Bootloader

Manufacturer:

Arduino

Datasheet:

Part Number:

Description:

Memory Cards MICRO SD CARD 1GB WITH SD ADAPTER

Manufacturer:

Arduino