z90102 ZiLOG Semiconductor, z90102 Datasheet - Page 17

z90102

Manufacturer Part Number

z90102

Description

40-pin Low-cost Digital Television Controller

Manufacturer

ZiLOG Semiconductor

Datasheet

1.Z90102.pdf

(36 pages)

Zilog

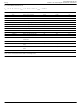

Program Memory. The program ROM size is 6 KB (Figure

14). The IRQ vector table is located in the lower address

space. The vector address is fetched after the correspond-

ing interrupt and program control is passed to the specified

DS97TEL1902

0000

0001

0002

0003

0004

0005

0006

0007

0008

0009

000A

000B

17FF

1800

FCFF

FDB4

FDB5

Address

000C

FBFF

FC32

FC33

FD00

FC00

FFFF

Hex

¯

¯

¯

¯

¯

¯

VSYNC IRQ1 (High Byte)

VSYNC IRQ1 (Low Byte)

On-Chip Program ROM

P31 IRQ2 (High Byte)

P30 IRQ3 (High Byte)

P31 IRQ2 (Low Byte)

P30 IRQ3 (Low Byte)

Reset Start Address

Memory Mapped I/O

T0 IRQ4 (High Byte)

T0 IRQ4 (Low Byte)

T1 IRQ5 (High Byte)

T1 IRQ5 (Low Byte)

Video Refresh RAM

IRQ0 (High Byte)

IRQ0 (Low Byte)

(6 KByte)

Reserved

Reserved

Reserved

Figure 14. Program Memory

PWM11 8-Bit Register (PWM11)

Horizontal Position (HOR_POS)

Bar Line Control (BAR_CNTRL)

PWM10 8-Bit Register (PWM10)

Display Attribute (DISP_ATTR)

PWM Output Port (PWM_OUT)

Vertical Position (VERT_POS)

PWM6 6-Bit Register (PWM6)

PWM7 6-Bit Register (PWM7)

PWM8 6-Bit Register (PWM8)

PWM9 8-Bit Register (PWM9)

PWM1 High 6-Bit (PWM1_HI)

vector address. IRQ1 vector is fixed to VSYNC interrupt re-

quest and occurs at the leading edge of the filtered VSYNC

input. Program memory start at address 000CH after re-

set.

PWM1 Low 8-Bit (PWM_LO)

OSD Control (OSD_CNTRL)

Row Space (ROW_SPACE)

Fade Position (FADE_POS)

PWM Mode (PWM_MODE)

Port 6 Input Port (PORT6)

Bar Position (BAR_POS)

Reserved

Reserved

Reserved

Reserved

40-Pin Low-Cost Digital Television Controller

Address

Hex

FC00

FC01

FC02

FC03

FC04

FC05

FC06

FC07

FC10

FC11

FC12

FC13

FC14

FC15

FC16

FC17

FC18

FC19

FC1A

FC1B

FC1C

FC1D

FC1E

FC1F

FC30

FC31

FC32

Z90102/90103/90104

Write

Only

17

1