hm5216805 Renesas Electronics Corporation., hm5216805 Datasheet - Page 20

hm5216805

Manufacturer Part Number

hm5216805

Description

16 M Lvttl Interface Sdram 100 Mhz/83 Mhz 1-mword 8-bit 2-bank/2-mword 4-bit 2-bank - Hitachi Semiconductor

Manufacturer

Renesas Electronics Corporation.

Datasheet

1.HM5216805.pdf

(60 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

hm5216805TT10M

Manufacturer:

HITACHI/日立

Quantity:

20 000

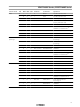

HM5216805 Series, HM5216405 Series

Mode Register Configuration

The mode register is set by the input to the address pins (A0 to A11) during mode register set cycles. The

mode register consists of five sections, each of which is assigned to address pins.

A11, A10, A9, A8 (OPCODE): The synchronous DRAM has two types of write modes. One is the burst

write mode, and the other is the single write mode. These bits specify write mode.

Burst read and BURST WRITE: Burst write is performed for the specified burst length starting from the

column address specified in the write cycle.

Burst read and SINGLE WRITE: Data is only written to the column address specified during the write

cycle, regardless of the burst length.

A7: Keep this bit Low at the mode register set cycle.

A6, A5, A4 (LMODE): These pins specify the CAS latency.

A3 (BT): A burst type is specified. When full-page burst is performed, only “sequential” can be selected.

A2, A1, A0 (BL): These pins specify the burst length.

20

A11

A11

0

X

X

X

A10

A10

OPCODE

X

X

X

0

A9

0

1

1

0

A9

A8

0

1

0

1

A8

Burst read and SINGLE WRITE

Burst read and burst write

Write mode

A6 A5 A4 CAS Latency

0

0

0

0

1

A7

0

R

R

0

0

1

1

X

A6

0

1

0

1

X

LMODE

A5

R

1

2

3

R

A4

A3

BT

A3

1

0 Sequential

Burst Type

Interleave

A2

BL

F.P. = Full Page (512: HM5216805)

R is Reserved (inhibit)

X: 0 or 1

A1

A0

A2 A1 A0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

(1024: HM5216405)

0

1

0

1

0

1

0

1

BT=0 BT=1

Burst Length

F.P.

1

2

4

8

R

R

R

1

2

4

8

R

R

R

R