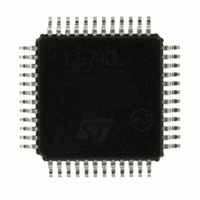

L6740LTR STMicroelectronics, L6740LTR Datasheet - Page 21

L6740LTR

Manufacturer Part Number

L6740LTR

Description

IC HYBRID CONTROLLERS 48TQFP

Manufacturer

STMicroelectronics

Datasheet

1.L6740LTR.pdf

(44 pages)

Specifications of L6740LTR

Applications

Hybrid Controllers

Voltage - Supply

9 V ~ 15 V

Current - Supply

20mA

Operating Temperature

0°C ~ 125°C

Mounting Type

Surface Mount

Package / Case

48-TQFP Exposed Pad, 48-eTQFP, 48-HTQFP, 48-VQFP

Number Of Outputs

2

Output Current

170 A

Input Voltage

13.2 V

Mounting Style

SMD/SMT

Maximum Operating Temperature

+ 125 C

Minimum Operating Temperature

0 C

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Voltage - Input

-

Lead Free Status / Rohs Status

Lead free / RoHS Compliant

Other names

497-6298-2

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

L6740LTR

Manufacturer:

ST

Quantity:

20 000

L6740L

5.4.2

5.4.3

PWROK de-assertion

Anytime PWROK de-asserts while EN is asserted, the controller uses the previously stored

Pre-PWROK Metal VID and regulates all the planes to that level performing an On-the-Fly

transition to that level.

PWRGOOD is treated appropriately being de-asserted in case the Pre-PWROK Metal VID

voltage is out of the initial voltage specifications.

PSI_L and efficiency optimization at light-load

PSI_L is an active-low flag (i.e. low logic level when asserted) that can be set by the CPU to

allow the VR to enter power-saving mode to maximize the system efficiency when in light-

load conditions. The status of the flag is communicated to the controller through the SVI bus

and it is reported on the PSI_L pin (open-drain).

The controller monitors the PSI_L pin also to define the PSI Strategy, that is the action

performed by the controller when PSI_L is asserted. According to

different voltage divider on PSI_L, it is possible to configure the device to disable one or two

phases while PSI_L is asserted. The device can also be configured to take no action so

phase number will not change after PSI_L assertion.

In case the phase number is changed, the device will disable one or two phases starting

from the highest one (i.e. if working at 3 phases, phase 3 will be disabled in case of 1 phase

reduction; phase 2 and 3 in case of 2phase reduction). To disable Phases, the controller will

set HiZ on the related PWM and re-configure internal phase-shift to maintain the

interleaving. Furthermore, the internal current-sharing will be adjusted to consider the phase

number reduction. ENDRV will remain asserted.

When PSI_L is de-asserted, the device will return to the original configuration.

Start-up is performed with all the configured phases enabled. In case of on-the-fly VID

transitions, the device will maintain the phase configuration set before.

PSI strategy (i.e. the voltage across PSI_L) is read and stored when PWRGOOD is

asserted at the end of the Soft-Start phase.

The phase number management is affected by the external driver selected.

●

●

Since PSI_L can be used to enable some of the external drivers connected, the status of the

pin is the logic AND between the PSI_L Flag and the status of the ENDRV pin: if the

controller wants to disable the external drivers pulling low ENDRV (because of protections

or simply for start-up synchronization) also PSI_L will be tied low.

NB section is not impacted by PSI_L status change.

efficiency improvement that can be achieved by enabling the PSI management.

If the external driver features the EN function, PSI_L can be tied directly to the EN of

the drivers of the phases that will be disabled.

Furthermore, in case the desired strategy is to work in single phase when 4phases are

configured, PSI_L can be tied also to the EN of the driver connected to Phase2

(apparently, from 4phases the max reduction would be to 2phase min.) in order to

disable also this phase during low-power mode.

If the external driver manages HiZ through the PWM input, PSI_L will be connected

only to the external divider used to set the strategy. The system can be down-graded to

single-phase only if configured for three phases.

Hybrid CPU support and CPU_TYPE detection

Figure 8

shows an example of the

Table

10, by programming

21/44