ISL62872HRUZ-T Intersil, ISL62872HRUZ-T Datasheet

ISL62872HRUZ-T

Specifications of ISL62872HRUZ-T

Available stocks

Related parts for ISL62872HRUZ-T

ISL62872HRUZ-T Summary of contents

Page 1

... Built-in voltage margin for system-level test CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. | 1-888-INTERSIL or 1-888-468-3774 Intersil (and design registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2008. All Rights Reserved All other trademarks mentioned are the property of their respective owners. FN6707.0 ...

Page 2

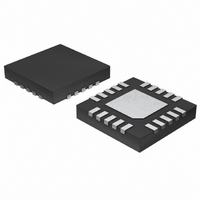

... SET1 9 Ordering Information PART NUMBER (Note) MARKING ISL62872HRUZ GAN ISL62872HRUZ -T* GAN ISL62871HRUZ GAM ISL62871HRUZ -T* GAM *Please refer to TB347 for details on reel specifications. NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020 ...

Page 3

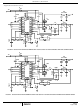

Block Diagram FB SREF SET0 SW2 *SET1 SW3 *SET2 *VID1 VID DECODER VID0 *ISL62872 ONLY GND INT 500mV FIGURE 1. SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM OF ISL62872, ISL62871 EN VCC POR RUN FAULT − COMP W ...

Page 4

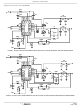

Application Schematics R VCC +5V C PVCC PGND 2 GND VID1 GPIO 5 VID0 6 SREF 7 SET0 8 SET1 SET1 SET2 SET3 FIGURE 2. ISL62872 APPLICATION SCHEMATIC WITH FOUR OUTPUT VOLTAGE SETPOINTS ...

Page 5

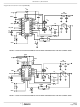

Application Schematics (Continued) R VCC +5V C PVCC GND GPIO VID0 3 SREF 4 R SET1 VCC GPIO FIGURE 4. ISL62871 APPLICATION SCHEMATIC WITH TWO OUTPUT VOLTAGE SETPOINTS AND DCR CURRENT SENSE R VCC +5V C PVCC ...

Page 6

Application Schematics (Continued) +5V C PVCC PGND 2 GND GPIO VID1 5 VID0 EXT_REF 6 SREF 7 SET0 8 SET1 9 VCC GPIO FIGURE 6. ISL62872 APPLICATION SCHEMATIC WITH EXTERNAL REFERENCE INPUT AND DCR CURRENT SENSE R ...

Page 7

... Junction Temperature Range .-55°C to +150°C Operating Temperature Range . . . . . . . . . . . . . . . .-10°C to +100°C Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . .-65°C to +150° -0. (DC) Pb-free Reflow Profile . . . . . . . . . . . . . . . . . . . . . . . . .see link below -0. (<10ns) http://www.intersil.com/pbfree/Pb-FreeReflow.asp Recommended Operating Conditions - 0.3V (DC BOOT Ambient Temperature Range .-10°C to +100°C BOOT Converter Input Voltage to GND . . . . . . . . . . . . . . . . . . 3.3V to 25V VCC, PVCC to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5V ± ...

Page 8

Electrical Specifications These specifications apply for T All typical specifications T +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued) PARAMETER EXTERNAL REFERENCE EXTREF Operating Voltage Range EXTREF Accuracy POWER GOOD PGOOD Pull-down Impedance ...

Page 9

Electrical Specifications These specifications apply for T All typical specifications T +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued) PARAMETER OVP Rising Threshold Voltage OVP Falling Threshold Voltage OTP Rising Threshold Temperature (Note ...

Page 10

BOOT (Pin 18) Positive input supply for the UGATE high-side MOSFET gate driver. The BOOT pin is internally connected to the cathode of the Schottky boot-strap diode. Connect an MLCC between the BOOT pin and the PHASE pin. VCC (Pin ...

Page 11

V where (x) is the first, second, third, or fourth setpoint SET(x) reference voltage where < V < V < V SET1 SET2 SET3 SET4 - V < V < V < V OUT1 OUT2 OUT3 OUT4 The ...

Page 12

The ISL62872 V setpoint is written as Equation 9: SET1 SET1 REF The ISL62872 V setpoint is written as Equation 10: SET2 ⎛ R SET1 ⋅ ⎜ -------------------------------------------------------------------- - SET2 REF ⎝ ...

Page 13

External Setpoint Reference The IC can use an external setpoint reference voltage as an alternative to VID-selected, resistor-programmed setpoints. This is accomplished by removing all setpoint programming resistors, connecting the SET0 pin to the VCC pin, and feeding the external ...

Page 14

Where the voltage-step delay the new setpoint voltage NEW - V is the setpoint voltage that V OLD from - I is the ±100µA setpoint voltage-step current; positive VS when V > V ...

Page 15

... V . UVTH Theory of Operation 3 The modulator features Intersil’s R Robust-Ripple- Regulator technology, a hybrid of fixed frequency PWM control and variable frequency hysteretic control. The PWM frequency is maintained at 300KHz under static continuous-conduction-mode operation within the entire specified envelope of input voltage, output voltage, and output load ...

Page 16

Efficiency is dramatically improved when the free-wheeling diode is replaced with a MOSFET that is turned on whenever the high-side MOSFET is turned off. This modification to the ...

Page 17

... It is assumed that the reader is familiar with many of the basic skills and techniques referenced in the 1V following. In addition to this guide, Intersil provides complete reference designs that include schematics, bills of materials, and example board layouts. Selecting the LC Output Filter The duty cycle of an ideal buck converter is a function of the input and the output voltage ...

Page 18

OCP faults. A DC/DC buck regulator must have output capacitance C into which ripple current I can flow. Current I P-P a corresponding ripple voltage V across C P-P sum of the ...

Page 19

Q = 100nC 0.6 GATE 0.4 0.2 20nC 0.0 0.0 0.1 0.2 0.3 0.4 0.5 DV BOOT_CAP FIGURE 15. BOOT CAPACITANCE vs BOOT RIPPLE VOLTAGE Driver Power Dissipation Switching power dissipation in ...

Page 20

Where the difference of the DC component of the VALLEY inductor current minus 1/2 of the inductor ripple current - I is the sum of the DC component of the inductor PEAK current plus 1/2 of the ...

Page 21

Typical Performance Curves 100 12. (A) OUT FIGURE 18. EFFICIENCY AT V 1.0 0.8 0.6 0 19V IN ...

Page 22

Typical Performance Curves EN PGOOD 10s FIGURE 24. SHUT-DOWN 12.6V LOAD = OPEN-CIRCUIT V OUT PHASE UGATE LGATE FIGURE 26. DCM STEADY-STATE OPERATION 12.6V 1.0V OUT 11ADC I OUT +10AµF ...

Page 23

Typical Performance Curves V OUT SREF VID0 VID1 FIGURE 30. SREF FALLING RESPONSE V = 12.6V 1.05V TO 950mV OUT 23 ISL62871, ISL62872 (Continued) VID0 VID1 FIGURE 31. SREF RISING RESPONSE = 10A OUT V OUT ...

Page 24

Package Outline Drawing L20.3.2x1.8 20 LEAD ULTRA THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE (UTQFN) Rev 0, 5/08 1.80 6 PIN 1 ID# (4X) 0.10 TOP VIEW (1 x 0.70 TYPICAL RECOMMENDED LAND PATTERN 24 ISL62871, ISL62872 ...

Page 25

... Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use ...