AD9516-4/PCBZ Analog Devices Inc, AD9516-4/PCBZ Datasheet - Page 44

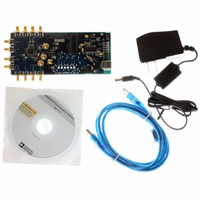

AD9516-4/PCBZ

Manufacturer Part Number

AD9516-4/PCBZ

Description

BOARD EVAL FOR AD9516-4 1.8GHZ

Manufacturer

Analog Devices Inc

Specifications of AD9516-4/PCBZ

Main Purpose

Timing, Clock Generator

Embedded

No

Utilized Ic / Part

AD9516-4

Primary Attributes

2 Inputs, 14 Outputs, 1.6GHz VCO

Secondary Attributes

CMOS, LVDS, LVPECL Output Logic, ADIsimCLK™ Graphical User Interface

Silicon Manufacturer

Analog Devices

Application Sub Type

PLL Clock Synthesizer

Kit Application Type

Clock & Timing

Silicon Core Number

AD9516-0, AD9516-1, AD9516-2

Silicon Family Name

AD9516-X

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

AD9516-4

Duty Cycle and Duty-Cycle Correction (Divider 3 and

Divider 4)

The same duty cycle and DCC considerations apply to Divider 3

and Divider 4 as to Divider 0, Divider 1, and Divider 2 (see the

Duty Cycle and Duty-Cycle Correction (0, 1, and 2) section);

however, with these channel dividers, the number of possible

configurations is even more complex.

Duty-cycle correction on Divider 3 and Divider 4 requires the

following channel divider conditions:

•

•

•

•

The possibilities for the duty cycle of the output clock from

Divider 3 and Divider 4 are shown in Table 40 through Table 44

Table 40. Divider 3, Divider 4 Duty Cycle; VCO Divider

Used; Duty Cycle Correction Off (DCCOFF = 1)

VCO

Divider

Even

Odd = 3

Odd = 5

Even

Odd

Even

Odd

Table 41. Divider 3, Divider 4 Duty Cycle; VCO Divider Not

Used; Duty Cycle Correction Off (DCCOFF = 1)

Input Clock

Duty Cycle

50%

X%

50%

X%

50%

X%

An even D

cycles).

An odd D

low cycles must be one greater than the number of high

cycles).

If only one divider is bypassed, it must be the second

divider, X.2.

If only one divider has an even divide by, it must be the

second divider, X.2.

X.Y

X.Y

N

1

1

Even, odd

Even, odd

Even, odd

Even, odd

N

1

1

Even, odd

Even, odd

1

Even, odd

Even, odd

X.1

X.1

must be set as M

must be set as M

+ M

+ M

D

D

X.1

X.1

X.1

X.1

+ 2

+ 2

N

1

1

1

1

1

Even, odd

Even, odd

N

1

1

1

1

Even, odd

Even, odd

X.2

X.2

X.Y

X.Y

+ M

+ M

= N

D

D

= N

X.2

X.2

X.2

X.2

X.Y

X.Y

+ 2

+ 2

+ 1 (the number of

(low cycles = high

50%

33.3%

40%

(N

(N

(N

(N

(N

(N

(N

(N

Output

Duty Cycle

50%

X%

(N

(N

(N

(N

(N

(N

(N

(N

Output Duty

X.1

X.1

X.1

X.1

X.2

X.2

X.2

X.2

X.1

X.1

X.1

X.1

X.2

X.2

X.2

X.2

+ 1)/

+ M

+ 1)/

+ M

+ 1)/

+ M

+ 1)/

+ M

+ 1)/

+ M

+ 1)/

+ M

+ 1)/

+ M

+ 1)/

+ M

Cycle

X.1

X.1

X.2

X.2

X.1

X.1

X.2

X.2

+ 2)

+ 2)

+ 2)

+ 2)

+ 2)

+ 2)

+ 2)

+ 2)

Rev. A | Page 44 of 80

Table 42. Divider 3, Divider 4 Duty Cycle; VCO Divider

Used; Duty Cycle Correction Is On (DCCOFF = 0); VCO

Divider Input Duty Cycle = 50%

VCO

Divider

Even

Odd

Even

Odd

Even

Odd

Even

Odd

Even

Odd

Even

Odd

Table 43. Divider 3, Divider 4 Duty Cycle; VCO Divider

Used; Duty Cycle Correction On (DCCOFF = 0); VCO

Divider Input Duty Cycle = X%

VCO

Divider

Even

Odd = 3

Odd = 5

Even

Odd

Even

Odd = 3

Odd = 5

Even

Odd

Even

Odd

Even

Odd = 3

Odd = 5

N

1

1

Even (N

Even (N

Odd (M

Odd (M

Even (N

Even (N

Odd (M

Odd (M

Odd (M

Odd (M

N

1

1

1

Even

(N

Even

(N

Odd

(M

Odd

(M

Odd

(M

Even

(N

Even

(N

Odd

(M

Odd

(M

Odd

(M

Odd

(M

Odd

(M

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

+ M

+ M

= M

= M

= M

= M

= N

= N

= N

= N

= N

= N

= N

= N

D

X.1

X.1

X.1

X.1

X.1

X.1

X.1

D

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

= N

= N

= N

= N

= N

= N

= M

= M

= M

= M

+ 1)

+ 1)

+ 1)

+ 1)

+ 1)

+ 1)

+ 1)

+ 1)

)

)

)

)

+ 2

+ 2

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

X.1

+ 1)

+ 1)

+ 1)

+ 1)

+ 1)

+ 1)

)

)

)

)

N

1

1

1

1

1

1

1

Even

(N

Even

(N

Even

(N

Even

(N

Odd

(M

Odd

(M

Odd

(M

1

X.2

X.2

X.2

X.2

X.2

X.2

X.2

X.2

N

1

1

1

1

1

1

Even (N

Even (N

Even (N

Even (N

Odd (M

Odd (M

+ M

= M

= M

= M

= M

= N

= N

= N

D

X.2

X.2

X.2

X.2

X.2

X.2

+ M

X.2

X.2

X.2

X.2

+ 2

+ 1)

+ 1)

+ 1)

)

)

)

)

X.2

X.2

D

X.2

X.2

X.2

X.2

X.2

X.2

= N

= N

= M

= M

= M

= M

+ 2

X.2

X.2

Output

Duty Cycle

50%

(1 + X%)/3

(2 + X%)/5

50%

50%

50%

(3N

(6N

(5N

(10N

50%

50%

50%

50%

50%

(6N

9N

(3(2N

(2N

(10N

15N

(5(2 N

(2 N

X.2

X.2

X.2

X.2

+ 1)

+ 1)

)

)

)

)

X.2

X.1

X.1

X.1

X.1

X.2

X.2

X.2

X.1

X.1

+ 13 + X%)/

N

X.1

+ 4 + X%)/

+ 9)

+ 7 + X%)/

+ 3))

X.1

N

+ 22 + X%)/

+ 3))

X.2

+ 15)

+ 3)

X.2

Output

Duty Cycle

50%

50%

50%

50%

50%

50%

50%

50%

50%

50%

50%

50%

+ 3)

+ 9N

+ 15N

X.1

X.1

+

+