QSK-62P PLUS BNS Solutions, QSK-62P PLUS Datasheet - Page 6

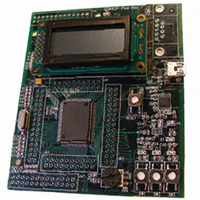

QSK-62P PLUS

Manufacturer Part Number

QSK-62P PLUS

Description

KIT QUICK START RENESAS 62P

Manufacturer

BNS Solutions

Series

M16C™r

Type

MCUr

Datasheet

1.QSK-62P_PLUS.pdf

(103 pages)

Specifications of QSK-62P PLUS

Contents

Board, Cable, CD

For Use With/related Products

M16C/62P

Lead Free Status / RoHS Status

Not applicable / Not applicable

Other names

867-1000

QSK-62P

QSK26A

QSK62P

QSK-62P

QSK26A

QSK62P

M16C/62P Group (M16C/62P, M16C/62PT)

Rev.2.41

REJ03B0001-0241

Table 1.3

NOTES:

CPU

Peripheral

Function

Electric

Characteristics

Flash memory

version

Operating Ambient Temperature

Package

1. I

2. IEBus is a registered trademark of NEC Electronics Corporation.

3. See Table 1.8 and 1.9 Product Code for the program and erase endurance, and operating ambient

4. All options are on request basis.

temperature.

In addition 1,000 times/10,000 times are under development as of Jul., 2005. Please inquire about a release

schedule.

2

C bus is a registered trademark of Koninklijke Philips Electronics N. V.

Jan 10, 2006

Performance Outline of M16C/62P Group (M16C/62P, M16C/62PT)(80-pin version)

Number of Basic Instructions

Minimum Instruction

Execution Time

Operating Mode

Address Space

Memory Capacity

Port

Multifunction Timer

Serial Interface

A/D Converter

D/A Converter

DMAC

CRC Calculation Circuit

Watchdog Timer

Interrupt

Clock Generation Circuit 4 circuits

Oscillation Stop

Detection Function

Voltage Detection Circuit Available (option

Supply Voltage

Power Consumption

Program/Erase Supply Voltage 3.3 ± 0.3V or 5.0 ± 0.5V

Program and Erase

Endurance

Page 4 of 96

Item

91 instructions

41.7ns(f(BCLK)=24MHz, VCC1=3.3 to 5.5V)

100ns(f(BCLK)=10MHz, VCC1=2.7 to 5.5V)

Single-chip mode

1 Mbyte

See

Input/Output : 70 pins, Input : 1 pin

Timer A : 16 bits x 5 channels (Timer A1 and A2 are internal timer),

Timer B : 16 bits x 6 channels (Timer B1 is internal timer)

2 channels

1 channel

2 channels

10-bit A/D converter: 1 circuit, 26 channels

8 bits x 2 channels

2 channels

CCITT-CRC

15 bits x 1 channel (with prescaler)

Internal: 29 sources, External: 5 sources, Software: 4 sources, Priority level: 7 levels

(*)Equipped with a built-in feedback resistor.

Stop detection of main clock oscillation, re-oscillation detection function

VCC1=3.0 to 5.5 V, (f(BCLK=24MHz)

VCC1=2.7 to 5.5 V, (f(BCLK=10MHz)

14 mA (VCC1=5V, f(BCLK)=24MHz)

8 mA (VCC1=3V, f(BCLK)=10MHz)

1.8µA (VCC1=3V, f(XCIN)=32kHz,

0.7µA (VCC1=3V, stop mode)

100 times (all area)

or 1,000 times (user ROM area without block A and block 1)

/ 10,000 times (block A, block 1)

-20 to 85°C,

-40 to 85°C

80-pin plastic mold QFP

Clock synchronous, UART, I

Clock synchronous, I

Clock synchronous (1 channel is only transmission)

Main clock generation circuit (*), Subclock generation circuit (*),

On-chip oscillator, PLL synthesizer

Table 1.4 to 1.7 Product List

wait mode)

Performance

(3)

M16C/62P

(4)

)

2

C bus

(1)

2

C bus

, IEBus

(3)

41.7ns(f(BCLK)=24MHz, VCC1=4.0 to 5.5V)

Absent

VCC1=4.0 to 5.5V, (f(BCLK=24MHz)

14 mA (VCC1=5V, f(BCLK)=24MHz)

2.0µA (VCC1=5V, f(XCIN)=32kHz,

0.8µA (VCC1=5V, stop mode)

5.0 ± 0.5V

T version : -40 to 85°C

V version : -40 to 125°C

(1)

, IEBus

(2)

wait mode)

(2)

M16C/62PT

(4)

1. Overview