QSK-62P PLUS BNS Solutions, QSK-62P PLUS Datasheet - Page 8

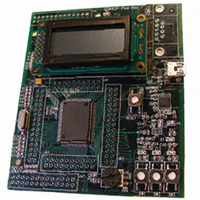

QSK-62P PLUS

Manufacturer Part Number

QSK-62P PLUS

Description

KIT QUICK START RENESAS 62P

Manufacturer

BNS Solutions

Series

M16C™r

Type

MCUr

Datasheet

1.QSK-62P_PLUS.pdf

(103 pages)

Specifications of QSK-62P PLUS

Contents

Board, Cable, CD

For Use With/related Products

M16C/62P

Lead Free Status / RoHS Status

Not applicable / Not applicable

Other names

867-1000

QSK-62P

QSK26A

QSK62P

QSK-62P

QSK26A

QSK62P

M16C/62P Group (M16C/62P, M16C/62PT)

Rev.2.41

REJ03B0001-0241

Figure 1.2

NOTES :

Port P0

1. ROM size depends on microcomputer type.

2. RAM size depends on microcomputer type.

3. To use a UART2, set the CRD bit in the U2C0 register to “1” (CTS/RTS function disabled).

4. There is no external connections for port P1, P4_4 to P4_7, P7_2 to P7_5 and P9_1 in 80-pin version.

Internal peripheral functions

Jan 10, 2006

Set the direction bits in these ports to “1” (output mode), and set the output data to “0” (“L”) using the program.

(8 bits X 2 channels)

Output (timer A): 5

Input (timer B): 6

Watchdog timer

8

D/A converter

(2 channels)

Timer (16-bit)

(15 bits)

DMAC

M16C/62P Group (M16C/62P, M16C/62PT) 80-pin version Block Diagram

Page 6 of 96

Port P2

UART or

clock synchronous serial I/O (2 channels)

UART

8

Expandable up to 26 channels)

M16C/60 series16-bit CPU core

CRC arithmetic circuit (CCITT )

(Polynomial : X

R0H

R1H

(10 bits

A/D converter

Port P3

R2

R3

FB

A0

A1

(4)

R0L

R1L

X

8

8 channels

16

+X

(1 channel)

12

Port P4

+X

5

+1)

4

INTB

PC

(3)

FLG

USP

SB

ISP

Port P5

Clock synchronous serial I/O

PLL frequency synthesizer

(8 bits

generation circuit

On-chip oscillator

8

System clock

XCIN-XCOUT

XIN-XOUT

X

2 channels)

Port P6

Memory

ROM

RAM

Multiplier

8

(2)

(1)

1. Overview