MPC8349E-MITX-GP Freescale Semiconductor, MPC8349E-MITX-GP Datasheet - Page 4

MPC8349E-MITX-GP

Manufacturer Part Number

MPC8349E-MITX-GP

Description

KIT REFERENCE PLATFORM MPC8349E

Manufacturer

Freescale Semiconductor

Series

PowerQUICC II™ PROr

Type

MPUr

Datasheets

1.MPC8349E-MITX-GP.pdf

(36 pages)

2.MPC8349E-MITX-GP.pdf

(2 pages)

3.MPC8349E-MITX-GP.pdf

(1 pages)

Specifications of MPC8349E-MITX-GP

Contents

Module and Misc Hardware

For Use With/related Products

MPC8349E

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

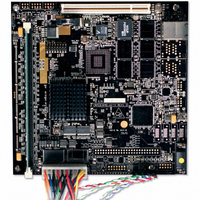

MPC8349E-mITX-GP Board

Figure 2

4

•

•

•

•

•

Hard reset is generated either by the COP/JTAG port or the MPC8349E.

Power-on reset is generated by the Maxim MAX811 device. When MR is deasserted and 3.3 V is

ready, the MAX811 internal timeout guarantees a minimum reset active time of 150 ms before

PORESET is deasserted. This circuitry guarantees a 150 ms PORESET pulse width after 3.3 V

reaches the right voltage level, and this meets the specification of the PORESET input of

MPC834x.

COP/JTAG port reset provides convenient hard-reset capability for a COP/JTAG controller. The

RESET line is available at the COP/JTAG port connector. The COP/JTAG controller can directly

generate the hard-reset signal by asserting this line low.

Push button reset interfaces the MR signal with a debounce capability to produce a manual master

reset of the processor card.

Soft reset is generated by the COP/JTAG port. Assertion of SRESET causes the MPC8349E to

abort all current internal and external transactions and set most registers to their default values.

HRESET from COP

shows the reset circuitry.

SRESET from COP

TRST from COP

MPC8349E-mITX-GP Reference Design Platform User’s Guide, Rev. 0

Figure 2. Reset Circuitry of the MPC8349E

3.3 V

MR

Preliminary—Subject to Change Without Notice

Push Button

MAX811

GND

PORESET to MPC8349E

FLASH

SRESET to MPC8349E

TRST to MPC8349E

10/100/1000 PHY

USB PHYs

MPC8349E

Freescale Semiconductor