AT90PWM3-16MQ Atmel, AT90PWM3-16MQ Datasheet - Page 139

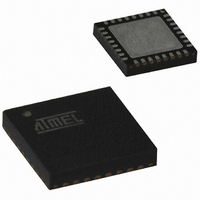

AT90PWM3-16MQ

Manufacturer Part Number

AT90PWM3-16MQ

Description

IC AVR MCU FLASH 8K 32QFN

Manufacturer

Atmel

Series

AVR® 90PWM Lightingr

Datasheet

1.AT90PWM3B-16SU.pdf

(361 pages)

Specifications of AT90PWM3-16MQ

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

27

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 11x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

32-QFN

Processor Series

AT90PWMx

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI, USART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

27

Number Of Timers

2

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT, ATAVRFBKIT, ATAVRISP2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 11 Channel

On-chip Dac

10 bit, 1 Channel

For Use With

ATSTK600-SOIC - STK600 SOCKET/ADAPTER FOR SOICATAVRMC200 - KIT EVAL FOR AT90PWM3 ASYNCATAVRFBKIT - KIT DEMO BALLAST FOR AT90PWM2ATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK520 - ADAPTER KIT FOR 90PWM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT90PWM3-16MQT

Manufacturer:

Atmel

Quantity:

1 325

- Current page: 139 of 361

- Download datasheet (7Mb)

16.5.3

16.6

16.6.1

16.7

4317J–AVR–08/10

Update of Values

Enhanced Resolution

Fifty Percent Waveform Configuration

Value Update Synchronization

When PSCOUTn0 and PSCOUTn1 have the same characteristics, it’s possible to configure the

PSC in a Fifty Percent mode. When the PSC is in this configuration, it duplicates the OCRn-

SBH/L and OCRnRBH/L registers in OCRnSAH/L and OCRnRAH/L registers. So it is not

necessary to program OCRnSAH/L and OCRnRAH/L registers.

To avoid unasynchronous and incoherent values in a cycle, if an update of one of several values

is necessary, all values are updated at the same time at the end of the cycle by the PSC. The

new set of values is calculated by sofware and the update is initiated by software.

Figure 16-11. Update at the end of complete PSC cycle.

The software can stop the cycle before the end to update the values and restart a new PSC

cycle.

New timing values or PSC output configuration can be written during the PSC cycle. Thanks to

LOCK and AUTOLOCK configuration bits, the new whole set of values can be taken into

account after the end of the PSC cycle.

When AUTOLOCK configuration is selected, the update of the PSC internal registers will be

done at the end of the PSC cycle if the Output Compare Register RB has been the last written.

The AUTOLOCK configuration bit is taken into account at the end of the first PSC cycle.

When LOCK configuration bit is set, there is no update. The update of the PSC internal registers

will be done at the end of the PSC cycle if the LOCK bit is released to zero.

The registers which update is synchronized thanks to LOCK and AUTOLOCK are PSOCn,

POM2, OCRnSAH/L, OCRnRAH/L, OCRnSBH/L and OCRnRBH/L.

See these register’s description starting on

When set, AUTOLOCK configuration bit prevails over LOCK configuration bit.

See “PSC 0 Configuration Register – PCNF0” on page 163.

Lamp Ballast applications need an enhanced resolution down to 50Hz. The method to improve

the normal resolution is based on Flank Width Modulation (also called Fractional Divider).

Cycles are grouped into frames of 16 cycles. Cycles are modulated by a sequence given by the

Software

PSC

Regulation Loop

Calculation

Cycle

With Set i

Cycle

With Set i

Cycle

With Set i

Writting in

PSC Registers

Cycle

With Set i

page

End of Cycle

Request for

an Update

162.

Cycle

With Set j

AT90PWM2/3/2B/3B

139

Related parts for AT90PWM3-16MQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC AVR MCU FLASH 8K 32SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 8K FLASH 16MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: