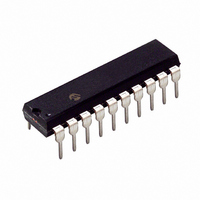

PIC16C770-I/P Microchip Technology, PIC16C770-I/P Datasheet - Page 215

PIC16C770-I/P

Manufacturer Part Number

PIC16C770-I/P

Description

IC MCU CMOS A/D 2K 20MHZ 20-DIP

Manufacturer

Microchip Technology

Series

PIC® 16Cr

Datasheets

1.PIC16C770-ISO.pdf

(220 pages)

2.PIC16C770-ISO.pdf

(6 pages)

3.PIC16C770-ISO.pdf

(8 pages)

Specifications of PIC16C770-I/P

Core Size

8-Bit

Program Memory Size

3.5KB (2K x 14)

Oscillator Type

Internal

Core Processor

PIC

Speed

20MHz

Connectivity

I²C, SPI

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

15

Program Memory Type

OTP

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

4 V ~ 5.5 V

Data Converters

A/D 6x12b

Operating Temperature

-40°C ~ 85°C

Package / Case

20-DIP (0.300", 7.62mm)

Controller Family/series

PIC16C

No. Of I/o's

16

Ram Memory Size

256Byte

Cpu Speed

20MHz

No. Of Timers

3

No. Of

RoHS Compliant

Core

PIC

Processor Series

PIC16C

Data Bus Width

8 bit

Maximum Clock Frequency

20 MHz

Data Ram Size

256 B

Data Rom Size

256 B

On-chip Adc

6 bit

Number Of Programmable I/os

16

Number Of Timers

3 bit

Operating Supply Voltage

2.5 V to 5.5 V

Mounting Style

Through Hole

Height

3.3 mm

Interface Type

I2C, SPI, SSP

Length

26.16 mm

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Supply Voltage (max)

5.5 V

Supply Voltage (min)

4 V

Width

6.35 mm

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

DVA16XP200 - ADAPTER ICE 20DIP/SOIC/SSOPAC164028 - MODULE SKT PROMATEII 20SOIC/DIP

Eeprom Size

-

Lead Free Status / Rohs Status

Details

Other names

PIC16C770I/P

SSPCON1 ........................................................................... 76

SSPCON2 ..................................................................... 69, 70

SSPEN ................................................................................ 67

SSPIF............................................................................ 18, 78

SSPM .................................................................................. 68

SSPOV.................................................................... 67, 77, 89

SSPSTAT.............................................................. 66, 76, 101

SSPSTAT Register ............................................................. 12

Stack ................................................................................... 22

Start bit (S) .......................................................................... 66

Start Condition Enabled bit, SAE ........................................ 69

STATUS Register ................................................. 14, 15, 128

Status Register ................................................................... 14

Stop bit (P) .......................................................................... 66

Stop Condition Enable bit ................................................... 69

Synchronous Serial Port ..................................................... 65

Synchronous Serial Port Enable bit, SSPEN ...................... 67

Synchronous Serial Port Interrupt ....................................... 18

Synchronous Serial Port Mode Select bits, SSPM ............. 68

T

T1CON ................................................................................ 13

T1CON Register ........................................................... 13, 47

T2CON Register ........................................................... 13, 51

Timer0

Timer1 ................................................................................. 47

2002 Microchip Technology Inc.

C Bit ............................................................................ 14

DC Bit.................................................................... 14, 15

IRP Bit......................................................................... 14

PD Bit.......................................................................... 14

RP Bits ........................................................................ 14

TO Bit.......................................................................... 14

Z Bit............................................................................. 14

T1CKPS Bits ............................................................... 47

T1OSCEN Bit.............................................................. 47

T1SYNC Bit................................................................. 47

TMR1CS Bit ................................................................ 47

TMR1ON Bit................................................................ 47

T2CKPS Bits ............................................................... 51

TMR2ON Bit................................................................ 51

TOUTPS Bits .............................................................. 51

Block Diagram............................................................. 45

Clock Source Edge Select (T0SE Bit)................... 15, 45

Clock Source Select (T0CS Bit)............................ 15, 45

Overflow Enable (T0IE Bit) ......................................... 16

Overflow Flag (T0IF Bit)...................................... 16, 128

Overflow Interrupt ............................................... 46, 128

Prescaler. See Prescaler, Timer0

Block Diagram............................................................. 48

Capacitor Selection..................................................... 49

Clock Source Select (TMR1CS Bit) ............................ 47

External Clock Input Sync (T1SYNC Bit) .................... 47

Module On/Off (TMR1ON Bit)..................................... 47

Oscillator ............................................................... 47, 49

Oscillator Enable (T1OSCEN Bit) ............................... 47

Overflow Enable (TMR1IE Bit).................................... 17

Overflow Interrupt ................................................. 47, 49

Prescaler. See Prescaler, Timer1

Special Event Trigger (ECCP) .............................. 49, 55

T1CON Register ......................................................... 47

TMR1H Register ......................................................... 47

TMR1L Register.......................................................... 47

Timer2

Timing Diagrams

TMR0 .................................................................................. 13

TMR0 Register.................................................................... 11

TMR1H ............................................................................... 13

TMR1H Register ................................................................. 11

TMR1L ................................................................................ 13

TMR1L Register.................................................................. 11

TMR2 .................................................................................. 13

TMR2 Register.................................................................... 11

TRISA Register........................................................... 12, 116

TRISB Register........................................................... 12, 116

TXREG ............................................................................... 13

U

Update Address, UA ........................................................... 66

USART

PIC16C717/770/771

Block Diagram ............................................................ 52

Postscaler. See Postscaler, Timer2

PR2 Register ........................................................ 51, 56

Prescaler. See Prescaler, Timer2

SSP Clock Shift .................................................... 51, 52

T2CON Register ......................................................... 51

TMR2 Register ........................................................... 51

TMR2 to PR2 Match Enable (TMR2IE Bit) ................. 17

TMR2 to PR2 Match Interrupt......................... 51, 52, 56

Acknowledge Sequence Timing ................................. 91

Baud Rate Generator with Clock Arbitration............... 85

BRG Reset Due to SDA Collision............................... 96

Brown-out Reset....................................................... 159

Bus Collision

Bus Collision During a Restart Condition

Bus Collision During a Restart Condition

Bus Collision During a Start Condition

Bus Collision During a Stop Condition........................ 98

Bus Collision for Transmit and Acknowledge ............. 94

Capture/Compare/PWM ........................................... 161

CLKOUT and I/O ...................................................... 157

External Clock Timing............................................... 157

I

I

I

I

Master Mode Transmit Clock Arbitration .................... 93

Power-up Timer ........................................................ 159

Repeat Start Condition ............................................... 86

Reset ........................................................................ 159

Slave Synchronization ................................................ 73

Start-up Timer........................................................... 159

Stop Condition Receive or Transmit ........................... 92

Time-out Sequence on Power-up..................... 125, 126

Timer0 ...................................................................... 160

Timer1 ...................................................................... 160

Wake-up from SLEEP via Interrupt .......................... 131

Watchdog Timer ....................................................... 159

Receive Enable (RCIE Bit) ................................... 17, 18

2

2

2

2

C Bus Data............................................................. 177

C Master Mode First Start bit timing ........................ 85

C Master Mode Reception timing............................. 90

C Master Mode Transmission timing ....................... 88

(Case 1).................................................................. 97

(Case2)................................................................... 97

(SCL = 0) ................................................................ 96

Start Condition Timing ........................................ 95

DS41120B-page 213