ATMEGA8515-16MU Atmel, ATMEGA8515-16MU Datasheet - Page 12

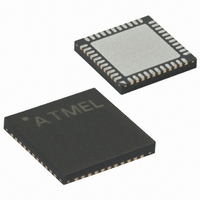

ATMEGA8515-16MU

Manufacturer Part Number

ATMEGA8515-16MU

Description

IC AVR MCU 8K 16MHZ 5V 44-QFN

Manufacturer

Atmel

Series

AVR® ATmegar

Specifications of ATMEGA8515-16MU

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

EBI/EMI, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

35

Program Memory Size

8KB (4K x 16)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-VQFN Exposed Pad

Processor Series

ATMEGA8x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI, USART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

35

Number Of Timers

2

Operating Supply Voltage

4.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

For Use With

ATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK500 - PROGRAMMER AVR STARTER KIT

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Data Converters

-

Lead Free Status / Rohs Status

Details

- Current page: 12 of 257

- Download datasheet (2Mb)

The X-register, Y-register, and

Z-register

Stack Pointer

12

ATmega8515(L)

The registers R26..R31 have some added functions to their general purpose usage.

These registers are 16-bit address pointers for indirect addressing of the Data Space.

The three indirect address registers X, Y, and Z are defined as described in Figure 5.

Figure 5. The X-, Y-, and Z-registers

In the different addressing modes these address registers have functions as fixed dis-

placement, automatic increment, and automatic decrement (see the Instruction Set

reference for details).

The Stack is mainly used for storing temporary data, for storing local variables and for

storing return addresses after interrupts and subroutine calls. The Stack Pointer Regis-

ter always points to the top of the Stack. Note that the Stack is implemented as growing

from higher memory locations to lower memory locations. This implies that a Stack

PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Inter-

rupt Stacks are located. This Stack space in the data SRAM must be defined by the

program before any subroutine calls are executed or interrupts are enabled. The Stack

Pointer must be set to point above $60. The Stack Pointer is decremented by one when

data is pushed onto the Stack with the PUSH instruction, and it is decremented by two

when the return address is pushed onto the Stack with subroutine call or interrupt. The

Stack Pointer is incremented by one when data is popped from the Stack with the POP

instruction, and it is incremented by two when address is popped from the Stack with

return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The num-

ber of bits actually used is implementation dependent. Note that the data space in some

implementations of the AVR architecture is so small that only SPL is needed. In this

case, the SPH Register will not be present.

X-register

Y-register

Z-register

Bit

Read/Write

Initial Value

SP15

SP7

R/W

R/W

15

7

0

0

15

7

R27 ($1B)

15

7

R29 ($1D)

15

7

R31 ($1F)

SP14

SP6

R/W

R/W

14

6

0

0

SP13

SP5

R/W

R/W

13

5

0

0

XH

YH

ZH

0

SP12

SP4

R/W

R/W

12

4

0

0

SP11

SP3

R/W

R/W

11

3

0

0

0

0

7

R26 ($1A)

7

R28 ($1C)

7

R30 ($1E)

SP10

R/W

R/W

SP2

10

2

0

0

R/W

R/W

SP9

SP1

9

1

0

0

XL

YL

ZL

0

R/W

R/W

SP8

SP0

2512K–AVR–01/10

8

0

0

0

SPH

SPL

0

0

0

0

0

Related parts for ATMEGA8515-16MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC AVR MCU 2.4GHZ XCEIVER 64QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA644/AT86RF230 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA644P/AT86RF230 QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA644P/AT86RF230 TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA1281/AT86RF230 64-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA1280/AT86RF230 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA1280/AT86RF100-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA2560V/AT86RF230-ZU

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA2561/AT86RF230 64-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet: