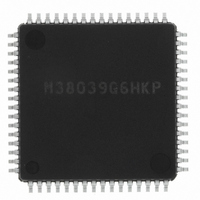

M38039G6HKP#U0 Renesas Electronics America, M38039G6HKP#U0 Datasheet - Page 33

M38039G6HKP#U0

Manufacturer Part Number

M38039G6HKP#U0

Description

IC 740/3803 MCU QZROM 64LQFP

Manufacturer

Renesas Electronics America

Series

740/38000r

Datasheet

1.M38039G4HHPU0.pdf

(105 pages)

Specifications of M38039G6HKP#U0

Core Processor

740

Core Size

8-Bit

Speed

16.8MHz

Connectivity

SIO, UART/USART

Peripherals

LED, PWM, WDT

Number Of I /o

56

Program Memory Size

24KB (24K x 8)

Program Memory Type

QzROM

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

1.8 V ~ 5.5 V

Data Converters

A/D 16x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

64-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

3803 Group (Spec.H QzROM version)

REJ03B0166-0113 Rev.1.13

Page 31 of 100

Fig 23. Interrupt sequence

Fig 24. Timing of interrupt request generation, interrupt request bit, and interrupt acceptance

Internal clock φ

SYNC

(1) The interrupt request bit for an interrupt request generated during period 1 is set to “1” at timing point IR1.

(2) The interrupt request bit for an interrupt request generated during period 2 is set to “1” at timing point IR1 or IR2.

The timing point at which the bit is set to “1” varies depending on conditions. When two or more interrupt

requests are generated during the period 2, each request bit may be set to “1” at timing point IR1 or IR2

separately.

Address bus

T1 T2 T3 : Interrupt acceptance timing points

IR1 IR2 : Timings points at which the interrupt request bit is set to “1”.

Note : Period 2 indicates the last φ cycle during one instruction cycle.

SYNC : CPU operation code fetch cycle

BL, BH: Vector address of each interrupt

AL, AH: Jump destination address of each interrupt

SPS

T1

Data bus

SYNC

: “00

WR

RD

(This is an internal signal that cannot be observed from the external unit.)

([SPS]

Instruction cycle

φ

Aug 21, 2009

16

1

” or “01

is a page selected by the stack page selection bit of CPU mode register.)

PC

Not used

16

”

2

IR1 T2

S,SPS

PC

Push onto stack

S-1,SPS S-2,SPS

Vector fetch

H

PC

L

Push onto stack

PS

Vector fetch

B

L

A

L

B

H

A

H

Execute interrupt

routine

A

L

,A

H

IR2 T3

Instruction cycle