COP8SGR728M8/NOPB National Semiconductor, COP8SGR728M8/NOPB Datasheet - Page 51

COP8SGR728M8/NOPB

Manufacturer Part Number

COP8SGR728M8/NOPB

Description

IC MCU 8BIT CMOS OTP 28SOIC

Manufacturer

National Semiconductor

Series

COP8™ 8SGr

Datasheet

1.COP8SGE728N8NOPB.pdf

(62 pages)

Specifications of COP8SGR728M8/NOPB

Core Processor

COP8

Core Size

8-Bit

Speed

15MHz

Connectivity

Microwire/Plus (SPI), UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

24

Program Memory Size

32KB (32K x 8)

Program Memory Type

OTP

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-SOIC (7.5mm Width)

Package

28SOIC W

Family Name

COP8

Maximum Speed

15 MHz

Operating Supply Voltage

3.3|5 V

Data Bus Width

8 Bit

Number Of Programmable I/os

40

Interface Type

USART

Number Of Timers

4

Maximum Clock Frequency

15 MHz

Data Ram Size

512 B

Height

2.34 mm

Length

17.91 mm

Maximum Operating Temperature

+ 85 C

Minimum Operating Temperature

- 40 C

Supply Voltage (max)

5.5 V

Supply Voltage (min)

2.7 V

Width

7.49 mm

For Use With

COP8SG-EPU - BOARD PROTOTYPE/TARGET COP8

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Lead Free Status / Rohs Status

Details

Other names

*COP8SGR728M8

COP8SGR728M8

COP8SGR728M8

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

COP8SGR728M8/NOPB

Manufacturer:

National

Quantity:

296

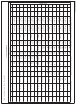

14.0 Instruction Set

INC

DEC

LAID

DCOR

RRC

RLC

SWAP

SC

RC

IFC

IFNC

POP

PUSH

VIS

JMPL

JMP

JP

JSRL

JSR

JID

RET

RETSK

RETI

INTR

NOP

A

A

A

A

A

A

A

A

Addr.

Addr.

Disp.

Addr.

Addr.

INCrement A

DECrement A

Load A InDirect from ROM

Decimal CORrect A

Rotate A Right thru C

Rotate A Left thru C

SWAP nibbles of A

Set C

Reset C

IF C

IF Not C

POP the stack into A

PUSH A onto the stack

Vector to Interrupt Service Routine

Jump absolute Long

Jump absolute

Jump relative short

Jump SubRoutine Long

Jump SubRoutine

Jump InDirect

RETurn from subroutine

RETurn and SKip

RETurn from Interrupt

Generate an Interrupt

No OPeration

(Continued)

51

A A + 1

A A − 1

A ROM (PU,A)

A BCD correction of A (follows ADC, SUBC)

C A7 … A0 C

C A7 … A0 C, HC A0

A7…A4

C 1, HC 1

C 0, HC 0

IF C is true, do next instruction

If C is not true, do next instruction

SP SP + 1, A [SP]

[SP] A, SP SP − 1

PU [VU], PL [VL]

PC ii (ii = 15 bits, 0 to 32k)

PC9…0 i (i = 12 bits)

PC PC + r (r is −31 to +32, except 1)

[SP] PL, [SP−1] PU,SP−2, PC ii

[SP] PL, [SP−1] PU,SP−2, PC9…0 i

PL ROM (PU,A)

SP + 2, PL [SP], PU [SP−1]

SP + 2, PL [SP],PU [SP−1],

skip next instruction

SP + 2, PL

[SP] PL, [SP−1] PU, SP−2, PC 0FF

PC PC + 1

A3…A0

[SP],PU [SP−1],GIE 1

www.national.com