LP3872ESX-3.3/NOPB National Semiconductor, LP3872ESX-3.3/NOPB Datasheet - Page 12

LP3872ESX-3.3/NOPB

Manufacturer Part Number

LP3872ESX-3.3/NOPB

Description

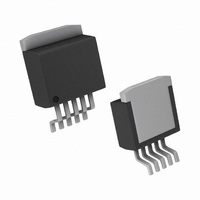

IC REG LDO 1.5A 3.3V TO-263-5

Manufacturer

National Semiconductor

Datasheet

1.LP3872EMP-3.3NOPB.pdf

(18 pages)

Specifications of LP3872ESX-3.3/NOPB

Regulator Topology

Positive Fixed

Voltage - Output

3.3V

Voltage - Input

Up to 7V

Voltage - Dropout (typical)

0.38V @ 1.5A

Number Of Regulators

1

Current - Output

1.5A (Max)

Operating Temperature

-40°C ~ 125°C

Mounting Type

Surface Mount

Package / Case

TO-263-5, D²Pak (5 leads + Tab), TO-263BA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Limit (min)

-

Other names

LP3872ESX-3.3

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LP3872ESX-3.3/NOPB

Manufacturer:

TI

Quantity:

12 000

www.national.com

Application Hints

PCB LAYOUT

Good PC layout practices must be used or instability can be

induced because of ground loops and voltage drops. The

input and output capacitors must be directly connected to the

input, output, and ground pins of the regulator using traces

which do not have other currents flowing in them (Kelvin

connect).

The best way to do this is to lay out C

device with short traces to the V

The regulator ground pin should be connected to the exter-

nal circuit ground so that the regulator and its capacitors

have a "single point ground".

It should be noted that stability problems have been seen in

applications where "vias" to an internal ground plane were

used at the ground points of the IC and the input and output

capacitors. This was caused by varying ground potentials at

these nodes resulting from current flowing through the

ground plane. Using a single point ground technique for the

regulator and it’s capacitors fixed the problem.

Since high current flows through the traces going into V

and coming from V

these pins so there is no voltage drop in series with the input

and output capacitors.

RFI/EMI SUSCEPTIBILITY

RFI (radio frequency interference) and EMI (electromagnetic

interference) can degrade any integrated circuit’s perfor-

mance because of the small dimensions of the geometries

inside the device. In applications where circuit sources are

present which generate signals with significant high fre-

quency energy content (

ensure that this does not affect the IC regulator.

If RFI/EMI noise is present on the input side of the regulator

(such as applications where the input source comes from the

output of a switching regulator), good ceramic bypass ca-

pacitors must be used at the input pin of the IC.

If a load is connected to the IC output which switches at high

speed (such as a clock), the high-frequency current pulses

required by the load must be supplied by the capacitors on

the IC output. Since the bandwidth of the regulator loop is

less than 100 kHz, the control circuitry cannot respond to

load changes above that frequency. This means the effective

output impedance of the IC at frequencies above 100 kHz is

determined only by the output capacitor(s).

In applications where the load is switching at high speed, the

output of the IC may need RF isolation from the load. It is

recommended that some inductance be placed between the

output capacitor and the load, and good RF bypass capaci-

tors be placed directly across the load.

PCB layout is also critical in high noise environments, since

RFI/EMI is easily radiated directly into PC traces. Noisy

circuitry should be isolated from "clean" circuits where pos-

sible, and grounded through a separate path. At MHz fre-

quencies, ground planes begin to look inductive and RFI/

EMI can cause ground bounce across the ground plane.

In multi-layer PCB applications, care should be taken in

layout so that noisy power and ground planes do not radiate

directly into adjacent layers which carry analog power and

ground.

OUT

, Kelvin connect the capacitor leads to

>

1 MHz), care must be taken to

(Continued)

IN

, V

OUT

IN

and C

, and ground pins.

OUT

near the

IN

12

OUTPUT NOISE

Noise is specified in two ways-

Spot Noise or Output noise density is the RMS sum of all

noise sources, measured at the regulator output, at a spe-

cific frequency (measured with a 1Hz bandwidth). This type

of noise is usually plotted on a curve as a function of fre-

quency.

Total output Noise or Broad-band noise is the RMS sum

of spot noise over a specified bandwidth, usually several

decades of frequencies.

Attention should be paid to the units of measurement. Spot

noise is measured in units µV/

noise is measured in µV(rms).

The primary source of noise in low-dropout regulators is the

internal reference. In CMOS regulators, noise has a low

frequency component and a high frequency component,

which depend strongly on the silicon area and quiescent

current. Noise can be reduced in two ways: by increasing the

transistor area or by increasing the current drawn by the

internal reference. Increasing the area will decrease the

chance of fitting the die into a smaller package. Increasing

the current drawn by the internal reference increases the

total supply current (ground pin current). Using an optimized

trade-off of ground pin current and die size, LP3872/LP3875

achieves low noise performance and low quiescent current

operation.

The total output noise specification for LP3872/LP3875 is

presented in the Electrical Characteristics table. The Output

noise density at different frequencies is represented by a

curve under typical performance characteristics.

SHORT-CIRCUIT PROTECTION

The LP3872 and LP3875 are short circuit protected and in

the event of a peak over-current condition, the short-circuit

control loop will rapidly drive the output PMOS pass element

off. Once the power pass element shuts down, the control

loop will rapidly cycle the output on and off until the average

power dissipation causes the thermal shutdown circuit to

respond to servo the on/off cycling to a lower frequency.

Please refer to the section on thermal information for power

dissipation calculations.

ERROR FLAG OPERATION

The LP3872/LP3875 produces a logic low signal at the Error

Flag pin when the output drops out of regulation due to low

input voltage, current limiting, or thermal limiting. This flag

has a built in hysteresis. The timing diagram in Figure 1

shows the relationship between the ERROR flag and the

output voltage. In this example, the input voltage is changed

to demonstrate the functionality of the Error Flag.

The internal Error flag comparator has an open drain output

stage. Hence, the ERROR pin should be pulled high through

a pull up resistor. Although the ERROR flag pin can sink

current of 1mA, this current is energy drain from the input

supply. Hence, the value of the pull up resistor should be in

the range of 10kΩ to 1MΩ. The ERROR pin must be

connected to ground if this function is not used. It should

also be noted that when the shutdown pin is pulled low, the

ERROR pin is forced to be invalid for reasons of saving

power in shutdown mode.

√

Hz or nV/

√

Hz and total output