ADSP-21368BBPZ-2A Analog Devices Inc, ADSP-21368BBPZ-2A Datasheet - Page 15

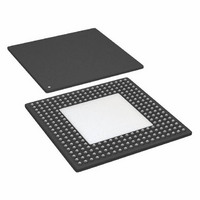

ADSP-21368BBPZ-2A

Manufacturer Part Number

ADSP-21368BBPZ-2A

Description

IC,DSP,32-BIT,CMOS,BGA,256PIN,PLASTIC

Manufacturer

Analog Devices Inc

Series

SHARC®r

Type

Floating Pointr

Datasheet

1.ADSP-21369KBPZ-2A.pdf

(60 pages)

Specifications of ADSP-21368BBPZ-2A

Interface

DAI, DPI

Clock Rate

333MHz

Non-volatile Memory

ROM (768 kB)

On-chip Ram

256kB

Voltage - I/o

3.30V

Voltage - Core

1.20V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

256-BGA Exposed Pad, 256-eBGA, 256-HBGA

Device Core Size

32/40Bit

Architecture

Super Harvard

Format

Floating Point

Clock Freq (max)

333MHz

Mips

333

Device Input Clock Speed

333MHz

Ram Size

256KB

Program Memory Size

768KB

Operating Supply Voltage (typ)

1.2/3.3V

Operating Supply Voltage (min)

1.14/3.13V

Operating Supply Voltage (max)

1.26/3.47V

Operating Temp Range

-40C to 85C

Operating Temperature Classification

Industrial

Mounting

Surface Mount

Pin Count

256

Package Type

SBGA

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADSP-21368BBPZ-2A

Manufacturer:

Analog Devices Inc

Quantity:

10 000

Table 8. Pin Descriptions (Continued)

1

2

The pull-up is always enabled on the ADSP-21367 and ADSP-21369 processors. The pull-up on the ADSP-21368 processor is only enabled on the processor with ID

Pull-up can be enabled/disabled, value of pull-up cannot be programmed.

Name

EMU

CLK_CFG

CLKIN

XTAL

RESET

RESETOUT

BOOT_CFG

BR

ID

RPBA

2–0

4–1

1–0

1–0

Type

O/T (pu)

I

I

O

I

O

I

I/O (pu)

I (pd)

I (pu)

1

1

State During/

After Reset

(ID = 00x)

Driven low/

driven high

Pulled high/

pulled high

Rev. E | Page 15 of 60 | July 2009

Description

Emulation Status. Must be connected to the ADSP-21367/ADSP-21368/

ADSP-21369 Analog Devices DSP Tools product line of JTAG emulator target board con-

nectors only.

Core/CLKIN Ratio Control. These pins set the start-up clock frequency. See the processor

hardware reference for a description of the clock configuration modes.

Note that the operating frequency can be changed by programming the PLL multiplier

and divider in the PMCTL register at any time after the core comes out of reset.

Local Clock In. Used with XTAL. CLKIN is the processor’s clock input. It configures the

processors to use either its internal clock generator or an external clock source. Connect-

ing the necessary components to CLKIN and XTAL enables the internal clock generator.

Connecting the external clock to CLKIN while leaving XTAL unconnected configures the

processor to use an external clock such as an external clock oscillator. CLKIN may not be

halted, changed, or operated below the specified frequency.

Crystal Oscillator Terminal. Used in conjunction with CLKIN to drive an external crystal.

Processor Reset. Resets the processor to a known state. Upon deassertion, there is a 4096

CLKIN cycle latency for the PLL to lock. After this time, the core begins program execution

from the hardware reset vector address. The RESET input must be asserted (low) at power-

up.

Reset Out. Drives out the core reset signal to an external device.

Boot Configuration Select. These pins select the boot mode for the processor. The

BOOT_CFG pins must be valid before reset is asserted. See the processor hardware

reference for a description of the boot modes.

External Bus Request. Used by the ADSP-21368 processor to arbitrate for bus master-

ship. A processor only drives its own BR

inputs) and monitors all others. In a system with less than four processors, the unused BR

pins should be tied high; the processor’s own BR

because it is an output.

Processor ID. Determines which bus request (BR

ID = 001 corresponds to BR

in single-processor systems. These lines are a system configuration selection that should

be hardwired or only changed at reset. ID = 101,110, and 111 are reserved.

Rotating Priority Bus Arbitration Select. When RPBA is high, rotating priority for the

ADSP-21368 external bus arbitration is selected. When RPBA is low, fixed priority is

selected. This signal is a system configuration selection which must be set to the same

value on every processor in the system.

ADSP-21367/ADSP-21368/ADSP-21369

1,

ID = 010 corresponds to BR

x

line (corresponding to the value of its ID2-0

4–1

x

line must not be tied high or low

) is used by the ADSP-21368 processor.

2

, and so on. Use ID = 000 or 001

2–0

= 00x

x