KSZ8841-16MBL Micrel Inc, KSZ8841-16MBL Datasheet - Page 13

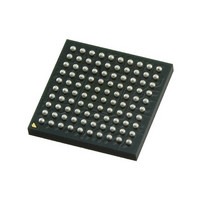

KSZ8841-16MBL

Manufacturer Part Number

KSZ8841-16MBL

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8841-16MBL.pdf

(105 pages)

Specifications of KSZ8841-16MBL

Controller Type

Ethernet Controller, MAC

Interface

Bus

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

100

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Supply

-

Lead Free Status / Rohs Status

Compliant

Other names

576-3075

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

KSZ8841-16MBL

Manufacturer:

MICREL/麦瑞

Quantity:

20 000

October 2007

Micrel, Inc.

Pin Number

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

EECS

EEEN

EEDO

EESK

Pin Name

SRDYN

INTRN

LDEVN

RDN

ARDY

CYCLEN

NC

DGND

VDDCO

VLBUSN

P1LED3

Type

Opu

Opd

Opd

Ipd

Opu

Opd

Ipd

Opd

Gnd

P

Ipd

Ipd

Opd

Opd

Opd

Pin Function

Synchronous Ready Not

Ready signal to interface with synchronous bus for both EISA-like and VLBus-like extend

accesses.

For VLBus-like mode, the falling edge of this signal indicates ready. This signal is

synchronous to the bus clock signal BCLK.

For burst mode (32-bit interface only), the KSZ8841M drives this pin low to signal wait

states.

Interrupt

Active Low signal to host CPU to indicate an interrupt status bit is set, this pin need an

external 4.7K pull-up resistor.

Local Device Not

Active Low output signal, asserted when AEN is Low and A15-A4 decode to the

KSZ8841M address programmed into the high byte of the base address register. LDEVN

is a combinational decode of the Address and AEN signal.

Read Strobe Not

Asynchronous read strobe, active Low.

EEPROM Chip Select

This signal is used to select an external EEPROM device.

Asynchronous Ready

ARDY may be used when interfacing asynchronous buses to extend bus access cycles. It

is asynchronous to the host CPU or bus clock. this pin need an external 4.7K pull-up

resistor.

Cycle Not

For VLBus-like mode cycle signal; this pin follows the addressing cycle to signal the

command cycle.

For burst mode (32-bit interface only), this pin stays High for read cycles and Low for write

cycles.

No Connect

Digital IO ground

1.2V digital core voltage output (internal 1.2V LDO power supply output), this 1.2V output

pin provides power to VDDC, VDDA and VDDAP pins. It is recommended this pin should

be connected to 3.3V power rail by a 100 ohm resistor for the internal LDO application

Note: Internally generated power voltage. Do not connect an external power supply to this

pin. This pin is used for connecting external filter (Ferrite bead and capacitors).

VLBus-like Mode

Pull-down or float: Bus interface is configured for synchronous mode.

Pull-up: Bus interface is configured for 8-bit or 16-bit asynchronous mode or EISA-like

burst mode.

EEPROM Enable

EEPROM is enabled and connected when this pin is pull-up.

EEPROM is disabled when this pin is pull-down or no connect.

Port 1 LED indicator

See the description in pins 3, 4, and 5.

EEPROM Data Out

This pin is connected to DI input of the serial EEPROM.

EEPROM Serial Clock

A 4

bus speed @ 125 MHz) serial output clock cycle to load configuration data from the serial

EEPROM.

µ

s (OBCR[1:0]=11 on-chip bus speed @ 25 MHz) or 800 ns (OBCR[1:0]=00 on-chip

13

KSZ8841-16/32 MQL/MVL/MBL

M9999-102207-1.6