KSZ8841-16MBL Micrel Inc, KSZ8841-16MBL Datasheet - Page 29

KSZ8841-16MBL

Manufacturer Part Number

KSZ8841-16MBL

Description

Single Ethernet Port + Generic (16-bit) Bus Interface( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8841-16MBL.pdf

(105 pages)

Specifications of KSZ8841-16MBL

Controller Type

Ethernet Controller, MAC

Interface

Bus

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

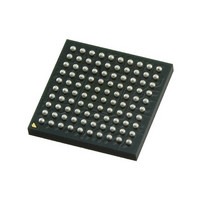

Package / Case

100-LFBGA

Operating Supply Voltage (typ)

3.3V

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

100

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Supply

-

Lead Free Status / Rohs Status

Compliant

Other names

576-3075

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

KSZ8841-16MBL

Manufacturer:

MICREL/麦瑞

Quantity:

20 000

Micrel, Inc.

KSZ8841-16/32 MQL/MVL/MBL

100BASE-TX Receive

The 100BASE-TX receiver function performs adaptive equalization, DC restoration, MLT3-to-NRZI conversion, data and

clock recovery, NRZI-to-NRZ conversion, de-scrambling, 4B/5B decoding, and serial-to-parallel conversion.

The receiving side starts with the equalization filter to compensate for inter-symbol interference (ISI) over the twisted pair

cable. Since the amplitude loss and phase distortion is a function of the cable length, the equalizer has to adjust its

characteristics to optimize performance. In this design, the variable equalizer makes an initial estimation based on

comparisons of incoming signal strength against some known cable characteristics, and then tunes itself for optimization.

This is an ongoing process and self-adjusts against environmental changes such as temperature variations.

Next, the equalized signal goes through a DC restoration and data conversion block. The DC restoration circuit is used to

compensate for the effect of baseline wander and to improve the dynamic range. The differential data conversion circuit

converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.

The clock recovery circuit extracts the 125MHz clock from the edges of the NRZI signal. This recovered clock is then used

to convert the NRZI signal into the NRZ format. This signal is sent through the de-scrambler followed by the 4B/5B

decoder. Finally, the NRZ serial data is converted to an MII format and provided as the input data to the MAC.

PLL Clock Synthesizer (Recovery)

The internal PLL clock synthesizer generates 125MHz, 62.5MHz, 41.66MHz, and 25MHz clocks by setting the on-chip

bus speed control register for KSZ8841M system timing. These internal clocks are generated from an external 25Mhz

crystal or oscillator.

Scrambler/De-scrambler (100BASE-TX Only)

The purpose of the scrambler is to spread the power spectrum of the signal to reduce electromagnetic interference (EMI)

and baseline wander.

Transmitted data is scrambled through the use of an 11-bit wide linear feedback shift register (LFSR). The scrambler

generates a 2047-bit non-repetitive sequence. Then the receiver de-scrambles the incoming data stream using the same

sequence as at the transmitter.

10BASE-T Transmit

The 10BASE-T driver is incorporated with the 100BASE-TX driver to allow for transmission using the same magnetics.

They are internally wave-shaped and pre-emphasized into outputs with a typical 2.4V amplitude. The harmonic contents

are at least 27dB below the fundamental frequency when driven by an all-ones Manchester-encoded signal.

10BASE-T Receive

On the receive side, input buffers and level detecting squelch circuits are employed. A differential input receiver circuit and

a phase-locked loop (PLL) perform the decoding function.

The Manchester-encoded data stream is separated into clock signal and NRZ data. A squelch circuit rejects signals with

levels less than 400mV or with short pulse widths to prevent noise at the RXP-or-RXM input from falsely triggering the

decoder. When the input exceeds the squelch limit, the PLL locks onto the incoming signal and the KSZ8841M decodes a

data frame.

The receiver clock is maintained active during idle periods in between data reception.

MDI/MDI-X Auto Crossover

To eliminate the need for crossover cables between similar devices, the KSZ8841M supports HP-Auto MDI/MDI-X and

IEEE 802.3u standard MDI/MDI-X auto crossover. HP-Auto MDI/MDI-X is the default.

The auto-sense function detects remote transmit and receive pairs and correctly assigns the transmit and receive pairs for

the KSZ8841M device. This feature is extremely useful when end users are unaware of cable types in addition to saving

on an additional uplink configuration connection. The auto-crossover feature can be disabled through the port control

registers.

October 2007

29

M9999-102207-1.6