KSZ8842-PMBL Micrel Inc, KSZ8842-PMBL Datasheet - Page 5

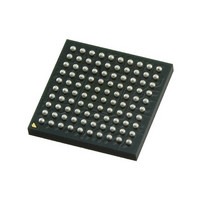

KSZ8842-PMBL

Manufacturer Part Number

KSZ8842-PMBL

Description

2-Port Ethernet Switch/Repeater + 32-bit/33MHz PCI Bus Interface ( )

Manufacturer

Micrel Inc

Datasheet

1.KSZ8842-PMBL.pdf

(119 pages)

Specifications of KSZ8842-PMBL

Controller Type

Ethernet Switch Controller

Interface

PCI

Voltage - Supply

3.1 V ~ 3.5 V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

100-LFBGA

Number Of Primary Switch Ports

2

Internal Memory Buffer Size

32

Operating Supply Voltage (typ)

3.3V

Fiber Support

Yes

Integrated Led Drivers

Yes

Phy/transceiver Interface

MII

Power Supply Type

Analog/Digital

Data Rate (typ)

10/100Mbps

Vlan Support

Yes

Operating Temperature (max)

70C

Operating Temperature (min)

0C

Mounting

Surface Mount

Jtag Support

No

Operating Supply Voltage (max)

3.5V

Operating Supply Voltage (min)

3.1V

Operating Temperature Classification

Commercial

Data Rate

100Mbps

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With

576-1636 - BOARD EVALUATION KSZ8842-PMQL

Current - Supply

-

Lead Free Status / RoHS Status

Supplier Unconfirmed, Lead free / RoHS Compliant

Other names

576-3089

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

KSZ8842-PMBL

Manufacturer:

TI

Quantity:

1 164

Company:

Part Number:

KSZ8842-PMBL AM

Manufacturer:

Micrel

Quantity:

1 053

Company:

Part Number:

KSZ8842-PMBL AM TR

Manufacturer:

Micrel Inc

Quantity:

10 000

Micrel, Inc.

Host Communication ...................................................................................................................................................... 35

PCI Configuration Registers .......................................................................................................................................... 39

PCI Control & Status Registers ..................................................................................................................................... 43

MAC/PHY and Control Registers ................................................................................................................................... 50

Switch Registers ............................................................................................................................................................. 52

October 2007

Configuration Interface.................................................................................................................................................. 33

EEPROM Interface ....................................................................................................................................................... 33

Loop back Support........................................................................................................................................................ 33

Host Communication Descriptor Lists and Data Buffers .............................................................................................. 35

Receive Descriptors (RDES0-RDES3) ......................................................................................................................... 35

Transmit Descriptors (TDES0-TDES3)......................................................................................................................... 37

Configuration ID Register (CFID Offset 00H) ............................................................................................................... 39

Command and Status Configuration Register (CFCS Offset 04H)............................................................................... 39

Configuration Revision Register (CFRV Offset 08H).................................................................................................... 41

Configuration Latency Timer Register (CFLT Offset 0CH)........................................................................................... 41

Configuration Base Memory Address Register (CBMA Offset 10H) ............................................................................ 42

Subsystem ID Register (CSID Offset 2CH) .................................................................................................................. 42

Configuration Interrupt Register (CFIT Offset 3CH) ..................................................................................................... 42

MAC DMA Transmit Control Register (MDTXC Offset 0x0000) ................................................................................... 43

MAC DMA Receive Control Register (MDRXC Offset 0x0004).................................................................................... 44

MAC DMA Transmit Start Command Register (MDTSC Offset 0x0008) ..................................................................... 45

MAC DMA Receive Start Command Register (MDRSC Offset 0x000C) ..................................................................... 46

Transmit Descriptor List Base Address Register (TDLB Offset 0x0010)...................................................................... 46

Receive Descriptor List Base Address Register (RDLB Offset 0x0014) ...................................................................... 46

Reserved (Offset 0x0018)............................................................................................................................................. 46

Reserved (Offset 0x001C) ............................................................................................................................................ 46

MAC Multicast Table 0 Register (MTR0 Offset 0x0020) .............................................................................................. 46

MAC Multicast Table 1 Register (MTR1 Offset 0x0024) .............................................................................................. 47

Interrupt Enable Register (INTEN Offset 0x0028) ........................................................................................................ 47

Interrupt Status Register (INTST Offset 0x002C) ......................................................................................................... 48

MAC Additional Station Address Low Register (MAAL0-15) ........................................................................................ 49

MAC Additional Station Address High Register (MAAH0-15)....................................................................................... 49

MAC Address Register Low (0x0200): MARL .............................................................................................................. 50

MAC Address Register Middle (0x0202): MARM ......................................................................................................... 50

MAC Address Register High (0x0204): MARH ............................................................................................................. 50

Reserved (Offset 0x0206 - 0x020A .............................................................................................................................. 51

On-Chip Bus Control Register (Offset 0x0210): OBCR................................................................................................ 51

EEPROM Control Register (Offset 0x0212): EEPCR................................................................................................... 51

Memory BIST Info Register (Offset 0x0214): MBIR ..................................................................................................... 52

Global Reset Register (Offset 0x0216): GRR............................................................................................................... 52

Switch ID and Enable Register (Offset 0x0400): SIDER .............................................................................................. 52

Switch Global Control Register 1 (Offset 0x0402): SGCR1 ......................................................................................... 53

Switch Global Control Register 2 (Offset 0x0404): SGCR2 ......................................................................................... 54

Switch Global Control Register 3 (Offset 0x0406): SGCR3 ......................................................................................... 55

Switch Global Control Register 4 (Offset 0x0408): SGCR4 ......................................................................................... 56

Switch Global Control Register 5 (Offset 0x040A): SGCR5 ......................................................................................... 56

Switch Global Control Register 6 (Offset 0x0410): SGCR6 ......................................................................................... 57

Switch Global Control Register 7 (0x0412): SGCR7 .................................................................................................... 58

Reserved (Offset 0x0414 - 0x046F) ............................................................................................................................. 58

MAC Address Register 1 (Offset 0x0470): MACAR1 ................................................................................................... 58

MAC Address Register 2 (Offset 0x0472): MACAR2 ................................................................................................... 58

MAC Address Register 3 (Offset 0x0474): MACAR3 ................................................................................................... 58

Reserved (Offset 0x0476 - 0x047F) ............................................................................................................................. 58

Priority Control Register 1 (Offset 0x0480): TOSR1..................................................................................................... 59

TOS Priority Control Register 2 (Offset 0x482): TOSR2 .............................................................................................. 59

TOS Priority Control Register 3 (Offset 0x484): TOSR3 .............................................................................................. 60

5

KSZ8842-PMQL/PMBL

M9999-100207-1.5