MT9M001C12STM Aptina LLC, MT9M001C12STM Datasheet - Page 22

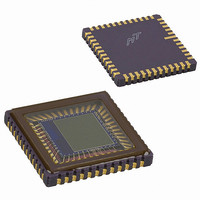

MT9M001C12STM

Manufacturer Part Number

MT9M001C12STM

Description

SENSOR IMAGE MONO CMOS 48-LCC

Manufacturer

Aptina LLC

Type

CMOS Imagingr

Datasheets

1.MT9M001C12STM.pdf

(35 pages)

2.MT9M001C12STM.pdf

(2 pages)

3.MT9M001C12STM.pdf

(28 pages)

Specifications of MT9M001C12STM

Pixel Size

5.2µm x 5.2µm

Active Pixel Array

1280H x 1024V

Frames Per Second

30

Voltage - Supply

3 V ~ 3.6 V

Package / Case

48-CLCC

Sensor Image Color Type

Monochrome

Sensor Image Size

1280x1024Pixels

Operating Supply Voltage (min)

3V

Operating Supply Voltage (typ)

3.3V

Operating Supply Voltage (max)

3.6V

Operating Temp Range

0C to 70C

Package Type

CLCC

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

48

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

557-1151

Q3930625

Q3990821

Q3930625

Q3990821

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MT9M001C12STM

Manufacturer:

MICRON

Quantity:

1 000

Part Number:

MT9M001C12STM

Manufacturer:

MICRON/镁光

Quantity:

20 000

Programmable Analog Offset Stage

Column and Row Mirror Image

Figure 11: Readout of Six Columns in Normal and Column Mirror Output Mode

Figure 12: Readout of Six Rows in Normal and Row Mirror Output Mode

Column and Row Skip

PDF: 09005aef81c2856f/Source: 09005aef80a3e031

MT9M001_DS_2.fm - Rev. F 5/06 EN

Reverse readout

Normal readout

The programmable analog offset stage corrects for analog offset that might be present in

the analog signal. The user would need to program register 0x62 appropriately to enable

the analog offset correction.

The lower eight bits (bit[7:0]) determines the absolute value of the analog offset to be

corrected and bit[8] determines the sign of the correction. When bit[8] is “1”, the sign of

the correction is negative and vice versa. The analog value of the correction relative to

the analog gain stage can be determined from the following formula:

By setting bit 14 of Reg0x20, the readout order of the columns will be reversed, as shown

in Figure 11.

By setting bits 15 of Reg0x20 the readout order of the rows will be reversed, as shown in

Figure 12.

By setting bit 3 of Reg0x20, only half of the columns set will be read out. An example is

shown in Figure 13. Only columns with bit 1 equal to “0” will be read out (xxxxxxx0x).

The row skip works in the same way and will only read out rows with bit 1 equal to “0.”

Row skip mode is enabled by setting bit 4 of Reg0x20. For both row and column skips, the

number of rows or columns read out will be half of what is set in Reg0x03 or Reg0x04,

respectively.

FRAME_VALID

Reverse readout

Normal readout

D

D

OUT

OUT

Analog offset (bit[8] = 0) = bit[7:0] x 2mV

Analog offset (bit[8] = 1) = - (bit[7:0] x 2mV)

D

D

LINE_VALID

OUT

OUT

9–D

9–D

9–D

9–D

OUT

OUT

OUT

OUT

0

0

0

0

MT9M001: 1/2-Inch Megapixel Digital Image Sensor

Row0

Row5

(9:0)

(9:0)

Col0

(9:0)

Col5

(9:0)

Row1

Row4

(9:0)

(9:0)

Col1

(9:0)

Col4

(9:0)

22

Row2

Row3

(9:0)

(9:0)

Col2

(9:0)

Col3

(9:0)

Micron Technology, Inc., reserves the right to change products or specifications without notice.

Row3

Row2

(9:0)

(9:0)

Col3

(9:0)

Col2

(9:0)

Row4

Row1

(9:0)

(9:0)

Col4

(9:0)

Col1

(9:0)

Row5

Row0

(9:0)

(9:0)

Col5

(9:0)

Col0

(9:0)

©2004 Micron Technology, Inc. All rights reserved.

Feature Description