AD9901KP-REEL Analog Devices Inc, AD9901KP-REEL Datasheet - Page 7

AD9901KP-REEL

Manufacturer Part Number

AD9901KP-REEL

Description

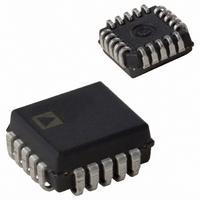

IC PHASE/FREQ DISCRIMR 20-PLCC

Manufacturer

Analog Devices Inc

Type

Digital Phase/Frequency Discriminatorr

Datasheet

1.AD9901KPZ.pdf

(8 pages)

Specifications of AD9901KP-REEL

Rohs Status

RoHS non-compliant

Pll

Yes

Input

CMOS, ECL, TTL

Output

CMOS, ECL, TTL

Number Of Circuits

1

Ratio - Input:output

2:1

Differential - Input:output

Yes/Yes

Frequency - Max

200MHz

Voltage - Supply

5V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

20-PLCC

Frequency-max

200MHz

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AD9901KP-REEL

Manufacturer:

ADI

Quantity:

500

REV. B

It is important to note that the slope of the transfer function is

constant near its midpoint. Many digital phase comparators have

an area near the lock point where their gain goes to zero, result-

ing in a “dead zone.” This causes increased phase noise (jitter) at

the lock point.

The AD9901 avoids this dead zone by shifting it to the end-

points of the transfer curve, as indicated in Figure 7. The in-

creased gain at either end increases the effective error signal to

pull the oscillator back into the linear region. This does not

affect phase noise, which is far more dependent upon lock region

characteristics.

It should be noted, however, that as frequency increases, the

linear range is decreased. At the ends of the detection range, the

reference and oscillator inputs approach phase alignment. At this

point, slew rate limiting in the detector effectively increases

phase gain. This decreases the linear detection by nominally

3.6 ns. Therefore, the typical detection range can be found by

calculating [(1/F – 3.6 ns)/(1/F)] 360 . As an example, at

200 MHz the linear phase detection range is 50 .

Away from lock, the AD9901 becomes a frequency discrimina-

tor. Any time either the reference or oscillator input occurs twice

before the other, the Frequency High or Frequency Low flip-flop

is clocked to logic LOW. This overrides the XOR output and

holds the output at the appropriate level to pull the oscillator

toward the reference frequency. Once the frequencies are within

the linear range, the phase detector circuit takes over again.

Combining the frequency discriminator with the phase detector

eliminates locking to a harmonic of the reference.

Figure 8 shows the effect of the “Frequency Low” flip-flop when

the oscillator frequency is much lower than the reference input.

The narrow pulses, which result from cycles when two positive

reference-input transitions occur before a positive VCO edge,

increase the dc mean value. Figure 9 illustrates the inverse effect

when the “Frequency High” flip-flop reacts to a much higher

VCO frequency.

Figure 10 shows the output waveform at lock for 50 MHz opera-

tion. This output results when the phase difference between

reference and oscillator is approximately – Rad.

AD9901 APPLICATIONS

The figure below illustrates a phase-locked loop (PLL) system

utilizing the AD9901. The first step in designing this type of

circuit is to characterize the VCO’s output frequency as a func-

tion of tuning voltage. The transfer function of the oscillator in

the diagram is shown in Figure 11.

Figure 8. AD9901 Output Waveform

(F

100

O

0%

90

10

<< F

500mV

I

)

200ns

Figure 9. AD9901 Output Waveform

(F

100

O

90

0%

10

>> F

500mV

I

)

–7–

Next, the range of frequencies over which the VCO is to operate

is examined to assure that it lies on a linear portion of the transfer

curve. In this case, frequencies from 100 MHz to 120 MHz

result from tuning voltages of approximately +1.5 V to +2.5 V.

Because the nominal output swing of the AD9901 is 0 V to –1.8 V,

an inverting amplifier with a gain of 2 follows the loop filter.

As shown in the illustration, a simple passive RC low-pass filter

made up of two resistors and a tantalum capacitor eliminates the

need for an expensive high speed op amp active-filter design. In

this passive-filter second-order-loop system, where n = 2, the

damping factor is equal to:

and the values for

stants R1C and R2C. The gain of 2 of the inverting stage, when

combined with the phase detector’s gain, gives:

With K

3.11

trated values of 30

diagram approximate these time constants.

The gain of the RC filter is:

Where K

For general information about phase-locked loop design, the

user is advised to consult the following references: Gardner,

Phase-Lock Techniques (Wiley); or Best, Phase Locked Loops

(McGraw-Hill).

K

V

n

O

= 0.5 [K

d

/V

= [K

= 0.572 V/RAD

10

O

I

O

= 115.2 MRAD/s/V,

= (1 + sR2C)/[1 + s(R1 + R2)C].

–4

200ns

165

155

145

135

125

115

105

K

95

85

75

65

s for the required damping factor of 0.7. The illus-

O

Figure 11. VCO Frequency vs. Voltage

d

K

–1

O

>>

d

K

/n(

d

/n(

0

n

1

1

, the system’s natural frequency:

+

and

VARACTORS TUNING VOLTAGE – Volts

1

(R1), 160

Figure 10. AD9901 Output Waveform

(F

+

2

)]

O

1

100

90

0%

10

2

1/2

2

= F

)]

are the low-pass filter’s time con-

1/2

= 4.5 kHz.

500mV

I

2

= 50 MHz)

[

1

equals 1.715s, and

2

(R2), and 10 F (C) in the

+ (n/K

3

O

K

4

d

)]

AD9901

5

2

equals

6

5ns