IDT79RC32V334-150BB IDT, Integrated Device Technology Inc, IDT79RC32V334-150BB Datasheet - Page 8

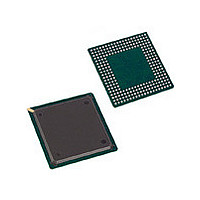

IDT79RC32V334-150BB

Manufacturer Part Number

IDT79RC32V334-150BB

Description

IC PROC 32BIT CORE 150MHZ 256BGA

Manufacturer

IDT, Integrated Device Technology Inc

Series

Interprise™r

Datasheet

1.IDT79RC32V334-100BB8.pdf

(30 pages)

Specifications of IDT79RC32V334-150BB

Processor Type

RISC 32-Bit

Speed

150MHz

Voltage

3.3V

Mounting Type

Surface Mount

Package / Case

256-BGA

Family Name

RC32300

Device Core

MIPS-II

Device Core Size

32b

Frequency (max)

150MHz

Instruction Set Architecture

MIPS-II

Supply Voltage 1 (typ)

3.3V

Operating Supply Voltage (max)

3.465V

Operating Supply Voltage (min)

3.135V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

256

Package Type

BGA

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Features

-

Lead Free Status / Rohs Status

Not Compliant

Other names

79RC32V334-150BB

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

IDT79RC32V334-150BB

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

Part Number:

IDT79RC32V334-150BB

Manufacturer:

IDT

Quantity:

20 000

Company:

Part Number:

IDT79RC32V334-150BBG

Manufacturer:

TI

Quantity:

900

Company:

Part Number:

IDT79RC32V334-150BBG

Manufacturer:

IDT

Quantity:

846

Company:

Part Number:

IDT79RC32V334-150BBG

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

Company:

Part Number:

IDT79RC32V334-150BBGI

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

Company:

Part Number:

IDT79RC32V334-150BBI

Manufacturer:

IDT, Integrated Device Technology Inc

Quantity:

10 000

sdram_cas_n

sdram_we_n

sdram_cke

sdram_cs_n[3:0]

sdram_s_n[1:0]

sdram_bemask_n

[3:0]

sdram_245_oe_n

sdram_245_dt_r_n

On-Chip Peripherals

dma_ready_n[1:0] /

dma_done_n[1:0]

pio[15:0]

timer_tc_n[0] /

timer_gate_n[0]

uart_rx[1:0]

IDT 79RC32334—Rev. Y

Name

Output

Output

Output

Output

Output

Output

Output

Output

Type

I/O

I/O

I/O

I/O

Status

Reset

State

related

See

pins

H

H

H

H

H

H

H

Z

Z

Z

Z

Capability

Strength

Drive

High

High

High

High

High

High

High

Low

Low

Low

Low

Low

SDRAM CAS Negated

SDRAM mode: Provides SDRAM CAS control signal to all SDRAM banks.

SDRAM WE Negated

SDRAM mode: Provides SDRAM WE control signal to all SDRAM banks.

SDRAM Clock Enable

SDRAM mode: Provides clock enable to all SDRAM banks.

SDRAM Chip Select Negated Bus

Recommend external pull-up.

SDRAM mode: Provides chip select to each SDRAM bank.

SODIMM mode: Provides upper select byte enables [7:4].

SDRAM SODIMM Select Negated Bus

SDRAM mode: Not used.

SDRAM SODIMM mode: Upper and lower chip selects.

SDRAM Byte Enable Mask Negated Bus (DQM)

SDRAM mode: Provides byte enables for each byte lane of all DRAM banks.

SODIMM mode: Provides lower select byte enables [3:0].

SDRAM FCT245 Output Enable Negated

Recommend external pull-up.

SDRAM mode: Controls output enable to optional FCT245 transceiver bank by asserting during both

reads and writes to any DRAM bank.

SDRAM FCT245 Direction Transmit/Receive

Recommend external pull-up.

Uses cpu_dt_r_n. See CPU Core Specific Signals below.

DMA Ready Negated Bus

Requires external pull-up.

Ready mode: Input pin for each general purpose DMA channel that can initiate the next datum in the cur-

rent DMA descriptor frame.

Done mode: Input pin for each general purpose DMA channel that can terminate the current DMA descrip-

tor frame.

dma_ready_n[0] 1st Alternate function PIO[1]; 2nd Alternate function: dma_done_n[0].

dma_ready_n[1] 1st Alternate function PIO[0]; 2nd Alternate function: dma_done_n[1].

Programmable Input/Output

General purpose pins that can each be configured as a general purpose input or general purpose output.

These pins are multiplexed with other pin functions:

uart_cts_n[0], uart_dsr_n[0], uart_dtr_n[0], uart_rts_n[0], pci_gnt_n[1], spi_mosi, spi_miso, spi_sck,

spi_ss_n, uart_rx[0], uart_tx[0], uart_rx[1], uart_tx[1], timer_tc_n[0], dma_ready_n[0], dma_ready_n[1].

Note that pci_gnt_n[1], spi_mosi, spi_sck, and spi_ss_n default to outputs at reset time. The others

default to inputs.

Timer Terminal Count Overflow Negated

Terminal count mode (timer_tc_n): Output indicating that the timer has reached its count compare value

and has overflowed back to 0.

Gate mode (timer_gate_n): input indicating that the timer may count one tick on the next clock edge.

1st Alternate function: PIO[2].

2nd Alternate function: timer_gate_n[0].

UART Receive Data Bus

UART mode: Each UART channel receives data on their respective input pin.

uart_rx[0] Alternate function: PIO[6].

uart_rx[1] Alternate function: PIO[4].

Table 1 Pin Description (Part 4 of 7)

8 of 30

Description

August 31, 2004