LS7061 LSI Computer Systems, Inc., LS7061 Datasheet

LS7061

Available stocks

Related parts for LS7061

LS7061 Summary of contents

Page 1

... Bytes of Data in Sequence in Multiple Counter Systems • LS7061, LS7063 (DIP); LS7061-S, LS7063-S (SOIC) - See Figures 1 & 2 DESCRIPTION: The LS7061/LS7063 is a MOS, 32 bit/dual 16 bit up counter. The IC includes 40 latches, multiplexer, eight three-state binary data output drivers and output cascading logic. DESCRIPTION OF OPERATION: 32 (16) BIT BINARY UP COUNTER - LS7061 (LS7063) The 32 (16) bit static ripple through counter increments on the negative edge of the input count pulse ...

Page 2

SCAN COUNTER AND DECODER The scan counter is reset to the least significant byte position (State 1) when SCAN RESET input is brought low for a mini- mum of 1µs. The scan counter is enabled for counting as long as ...

Page 3

ABSOLUTE MAXIMUM RATINGS: PARAMETER StorageTemperature Operating Temperature Voltage (any pin ELECTRICAL CHARACTERISTICS +5V ± 0˚ 70˚C unless otherwise noted PARAMETER SYMBOL Power ...

Page 4

... Count Pulse Width (All Count Inputs) Count Rise & Fall time (Pins 2, 16) Count Ripple Time (Pin 2 - LS7061) Count Ripple Time (Pin 13 - LS7061) (Pins LS7063) RESET Pulse Width (All Counter Stages Fully Reset) RESET Removal Time (Reset Removed From All Counter Stages) ...

Page 5

RESET COUNT t LOAD RESET SC ENABLE SCAN RESET SCAN 7061/63-012703-5 t RPW CPW RSCR CPW FIGURE 4. COUNTER TIMING DIAGRAM OUTPUT DATA BUS RESET SC FIGURE 5. ...

Page 6

SCAN RESET ENABLE SCAN CASCADE ENABLE A CASCADE ENABLE B CASCADE ENABLE C (END OF SCAN) DATA BYTE ON BUS PACKAGE FIGURE 7. APPLICATION EXAMPLE: HIGH SPEED DIFFERENTIAL ENERGY ANALYZER RADIATION P ...

Page 7

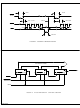

... BIT LATCH (COUNT DATA IN 7061/63-012703-7 FIGURE 8A. LS7061 BLOCK DIAGRAM 6 STATE STATIC SCAN COUNTER AND DECODER C SC (STOPS IN STATE 6 UNTIL SCAN RESET CAUSES RESET TO STATE ONE ST2 ST4 ST5 ST1 ST3 8 BIT MUX BUS MUX MUX G GATE GATE 8 BIT LATCH 8 BIT LATCH ...