AD9639 Analog Devices, Inc., AD9639 Datasheet - Page 21

AD9639

Manufacturer Part Number

AD9639

Description

Quad, 12-bit, 170 Msps/210 Msps Serial Output 1.8 V Adc

Manufacturer

Analog Devices, Inc.

Datasheet

1.AD9639.pdf

(36 pages)

DIGITAL OUTPUTS

Serial Data Frame

The AD9639 digital output complies with the JEDEC Standard

No. 204 (JESD204), which describes a serial interface for data

converters. JESD204 uses 8B/10B encoding as well as optional

scrambling. K28.5 and K28.7 comma symbols are used for frame

synchronization. The receiver is required to lock onto the serial

data stream and recover the clock with the use of a PLL. (Refer

to IEEE Std 802.3-2002, Section 3, for a complete 8B/10B and

comma symbol description.)

The 8B/10B encoding works by taking eight bits of data (an

octet) and encoding them into a 10-bit symbol. In the AD9639,

the 12-bit converter word is broken into two octets. Bit 11

through Bit 4 are in the first octet. The second octet contains

Bit 3 through Bit 0 and four tail bits. The MSB of the tail bits can

also be used to indicate an out-of-range condition. The tail bits

are configured using the JESD204 register, Address 0x033[3].

TIME

TRANSMITTER

FROM

DATA

ADC

FROM

WORD 1[3:0], TAIL BITS[3:0]

WORD 0[3:0],TAIL BITS[3:0]

WORD 0[11:4]

WORD 1[11:4]

DECODER

(ADD TAIL BITS)

8B/10B

ASSEMBLER

Figure 52. 12-Bit Data Transmission with Tail Bits

FRAME

Figure 53. Required Receiver Data Path

Figure 51. ADC Data Output Path

Rev. 0 | Page 21 of 36

DESCRAMBLER

1 + x

SCRAMBLER

1 + x

14

+ x

14

15

+ x

15

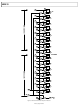

The two resulting octets are optionally scrambled and encoded

into their corresponding 10-bit code. The scrambling function

is controlled by the JESD204 register, Address 0x033[0]. Figure 51

shows how the 12-bit data is taken from the ADC, the tail bits are

added, the two octets are scrambled, and the octets are encoded

into two 10-bit symbols. Figure 52 illustrates the data format.

The scrambler uses a self-synchronizing polynomial-based

algorithm defined by the equation 1 + x

in the receiver should be a self-synchronizing version of the

scrambler polynomial. A 16-bit parallel implementation is

shown in Figure 54.

Refer to JEDEC Standard No. 204-April 2006, Section 5.1, for

complete transport layer and data format details and Section 5.2

for a complete explanation of scrambling and descrambling.

SYMBOL 0[9:0]

SYMBOL 1[9:0]

SYMBOL 2[9:0]

SYMBOL 3[9:0]

ALIGNMENT

FRAME

ENCODER

8B/10B

TO

RECEIVER

DATA

OUT

FRAME 0

FRAME 1

14

+ x

15

. The descrambler

AD9639