upd17107 Renesas Electronics Corporation., upd17107 Datasheet

upd17107

Available stocks

Related parts for upd17107

upd17107 Summary of contents

Page 1

BIT SINGLE-CHIP MICROCONTROLLER The PD17107(A1 tiny microcontroller consisting of 1K-byte (512 input/output ports. The 17K architecture, which uses general registers to directly manipulate data memory, is employed for effective programming. Every instruction is 1 word long, consisting ...

Page 2

FUNCTIONS Item 1K byte (512 ROM 16 4 bits RAM 1 level Stack 11 (N-ch open-drain output ports: 3) Number of I/O ports RC oscillation System clock ( 128 62.5 kHz ...

Page 3

BLOCK DIAGRAM N-ch open drain P0B /RLS 0 HALT P0B /RLS 1 STOP P0B P0B 2 CMOS P0C 0 P0C 1 P0C P0C 2 P0C 3 CMOS P0D 0 P0D 1 P0D P0D 2 P0D 3 RESET V DD GND ...

Page 4

PIN FUNCTIONS Pin functions • Port pins Pin I/O P0B /RLS I/O For releasing the HALT mode 0 HALT P0B /RLS For releasing the STOP mode 1 STOP P0B • N-ch open-drain 3-bit I/O port (port 0B) 2 • A ...

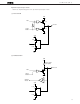

Page 5

Equivalent input/output circuits Below are simplified diagrams of the equivalent input/output circuits. (1) P0C and P0D Data Output disable P-ch N-ch (2) P0B and P0B 0 1 Data Output disable Stand-by release P- OUT ...

Page 6

P0B 2 Data Output disable V P-ch N-ch (4) RESET Pull-up resistor (mask option OUT N- Pull-up resistor (mask option) PD17107(A1) ...

Page 7

HANDLING UNUSED PINS When connecting unused pins, the following conditions and handling are recommended: Pin Input Port P0C, P0D mode P0B Pull-up resistors that can be specified by the mask option are not incorporated. Pull-up resistors that can be specified ...

Page 8

PROGRAM COUNTER (PC) ...................................................................................................... 1.1 CONFIGURATION OF THE PROGRAM COUNTER (PC) ............................................................ 1.2 FUNCTIONS OF THE PROGRAM COUNTER (PC) ..................................................................... 2. STACK ......................................................................................................................................... 3. PROGRAM MEMORY (ROM) ..................................................................................................... 4. DATA MEMORY (RAM) .............................................................................................................. 4.1 CONFIGURATION OF THE DATA MEMORY ...

Page 9

PORTS ......................................................................................................................................... 6.1 PORT 0B (P0B /RLS , P0B 0 HALT 6.2 PORT 0C (P0C TO P0C ) .............................................................................................................. 0 3 6.3 PORT 0D (P0D TO P0D ) .............................................................................................................. 0 3 6.4 NOTES ON MANIPULATING PORT REGISTERS ....................................................................... 7. ...

Page 10

PROGRAM COUNTER (PC) 1.1 CONFIGURATION OF THE PROGRAM COUNTER (PC) As shown in Fig. 1-1, the program counter is a 9-bit binary counter 1.2 FUNCTIONS OF THE PROGRAM COUNTER (PC) The program counter specifies the ...

Page 11

STACK Stack of the PD17107(A1 register in which the return address of a program is saved when a subroutine call instruction is executed. One level of address stack is provided. Fig. 2-1 shows the relationship between the ...

Page 12

PROGRAM MEMORY (ROM) Fig. 3-1 shows the program memory (ROM) configuration. As shown in the figure, the program memory has 512 words by 16 bits. The program memory has been addressed in units of 16 bits. The addresses 0000H ...

Page 13

DATA MEMORY (RAM) The data memory (RAM) stores data of arithmetic/logic and control operations. Data can be always written to or read from it by means of instructions. 4.1 CONFIGURATION OF THE DATA MEMORY (RAM) Fig. 4-1 shows the ...

Page 14

Functions of the System Register The system register controls the CPU. The program status word (PSWORD) is the only system register in the PD17107(A1). Address 74H 75H 76H 77H Data Addresses 74H to 7DH are ...

Page 15

Fig. 4-3 Configuration of the Program Status Word Address 7EH Address 7FH Bit 0 Bit 3 PSW BCD CMP CY Z Comparison instructions (SKE, SKNE, SKGE, or SKLT) do not change the state of the CY flag, but an arithmetic ...

Page 16

Conditions When arithmetic operation results in 0 When arithmetic operation results in a non-zero value While CMP arithmetic operation results in 0H when the value of the Z flag is 1, the Z flag does not ...

Page 17

ALU BLOCK The ALU is used for performing arithmetic operations, logical operations, bit evaluations, comparison evaluations, and rotations on 4-bit data. 5.1 ALU BLOCK CONFIGURATION Fig. 5-1 shows the configuration of the ALU block. As shown in Fig. 5-1, ...

Page 18

Fig. 5-1 Configuration of the ALU Block Temporary register A Address 7EH Program status word Name (PSWORD) Bit Flag BCD CMP Status flip-flop BCD CMP flag flag flip-flop flip-flop 18 Data bus Temporary Status register B flip-flop ...

Page 19

PD17107(A1) 19 ...

Page 20

Table 5-1 List of ALU Instructions (1/2) ALU function Instruction ADD r, m (r) (r) + (m) Arithme- Addi- tion tic opera- ADD m, #n4 (m) tions ADDC r, m (r) ( ADDC m, #n4 (m) ...

Page 21

Table 5-1 List of ALU Instructions (2/2) ALU function Operation depending on the program status word (PSWORD) Arithmetic operation Value in Value in CMP flag BCD flag Logical operations Don’t care Don’t care (maintained) (maintained) Bit ...

Page 22

Functions of Temporary Registers A and B Temporary registers A and B are needed for processing of 4-bit data. These registers are used for temporary storage of the first and second data operands of an instruction. 5.2.3 Functions of ...

Page 23

Performing Operations in 4-Bit Binary When the BCD flag is set to 0, arithmetic operations are performed in 4-bit binary. 5.2.5 Performing Operations in BCD When the BCD flag is set to 1, arithmetic operations are performed in BCD. ...

Page 24

Performing Operations in the ALU Block When arithmetic operations, logical operations, bit evaluations, comparison evaluations or rotations in a program are executed, the first data operand is stored in temporary register A and the second data operand is stored ...

Page 25

ARITHMETIC OPERATIONS (ADDITION AND SUBTRACTION IN 4-BIT BINARY AND BCD) As shown in Table 5-3, arithmetic operations consist of addition, subtraction, addition with carry, and subtraction with borrow. These instructions are ADD, ADDC, SUB, and SUBC. The ADD, ADDC, ...

Page 26

Addition and Subtraction When BCD = 1 and CMP = 0 BCD operations are performed. The result of the operation is stored in the general register (or data memory). When the result of the operation is greater than 1001B ...

Page 27

Warnings Concerning Use of Arithmetic Operations When performing arithmetic operations with the PSW (address 7FH), note the followings: When the CMP flag is cleared (0) and an arithmetic operation is performed on the PSW, the result is stored in ...

Page 28

BIT EVALUATIONS As shown in Table 5-6, there are both TRUE (1) and FALSE (0) bit evaluation instructions. The SKT instruction skips the next instruction when a bit is evaluated as TRUE (1) and the SKF instruction skips the ...

Page 29

FALSE (0) Bit Evaluation The FALSE (0) bit evaluation instruction (SKF m, #n) is used to determine whether or not the bits specified the four bits of data memory m are FALSE (0). When all bits ...

Page 30

Evaluation The "equal" evaluation instruction (SKE m, #n4) is used to determine if immediate data and the contents of a location in data memory are equal. This instruction causes the next instruction to be skipped when the immediate ...

Page 31

Than or Equal" Evaluation The "greater than or equal" evaluation instruction (SKGE m, #n4) is used to determine if the contents of a location in data memory is a value greater than or equal to the value of ...

Page 32

ROTATIONS There are rotation instructions for rotation to the right and for rotation to the left. The RORC instruction is used for rotation to the right. The RORC instruction can only be used with the general register. Rotation using ...

Page 33

Rotation to the Left Rotation to the left is performed by using the addition instruction, "ADDC r, m". Example MOV PSW, #0000B ; Resets CY flag to 0. MOV R1, #1000B ; Most significant bit MOV R2, #0100B MOV ...

Page 34

PORTS 6.1 PORT 0B (P0B /RLS , P0B /RLS 0 HALT 1 Port three-bit input/output port. Only N-ch open-drain outputs appear on the pins of port 0B. The N-ch open-drain output mode allows application of 9 ...

Page 35

Fig. 6-1 Port Register Map Row address Port register 7X 70H 71H Address Bit symbol ...

Page 36

NOTES ON MANIPULATING PORT REGISTERS The states of the I/O port pins of the PD17107(A1) can be read even when the port pins have been set to output mode. When a port register is manipulated with a built-in macro ...

Page 37

STANDBY FUNCTIONS The PD17107(A1) provides two standby modes, the HALT mode and the STOP mode. 7.1 HALT MODE The HALT mode stops the program counter (PC) while allowing the system clock to continue operating. The HALT mode can be ...

Page 38

Table 7-2 Conditions for Setting/Releasing the STOP Mode STOP 000XB 4-bit data in the operand X 0 After executing a STOP instruction, the system enters the STOP mode unconditionally. All peripheral circuits are placed in the same initial state as ...

Page 39

Fig. 7-2 Releasing the HALT Mode by High-Level Input to the P0B HALT instruction Standby release signal (P0B ) 0 Operation mode Clock Fig. 7-3 Releasing the STOP Mode by RESET Input STOP instruction RESET Operation mode STOP mode Oscillation ...

Page 40

RESET FUNCTION 8.1 RESET FUNCTION A low-level signal, applied to the RESET pin, resets the system, then the hardware is initialized. The system clock oscillates as long as the power supply voltage is supplied, even if a low-level signal ...

Page 41

RESERVED WORDS USED IN ASSEMBLY LANGUAGE 9.1 MASK-OPTION PSEUDO INSTRUCTIONS Source programs in the assembly language for the PD17107(A1) must include mask-option pseudo instructions to select pin options this, be sure to catalog the D17107.OPT file in ...

Page 42

The coding format of OPTRES is as follows. Format: Symbol Mnemonic [label:] OPTRES Example The following mask options are set in a PD17107(A1) source file to be assembled: P0B : Pull-up, P0B : Open, P0B 2 1 RESET: Pull-up ;17107(A1) ...

Page 43

RESERVED SYMBOLS Table 9-2 lists the reserved symbols defined in the PD17107(A1) device file (AS17103). Name Attribute FLG P0B0 FLG P0B1 FLG P0B2 Note FLG P0B3 FLG P0C0 FLG P0C1 FLG P0C2 FLG P0C3 P0D0 FLG FLG P0D1 FLG ...

Page 44

INSTRUCTION SET 10.1 INSTRUCTION SET LIST BIN HEX ADD SUB ADDC SUBC 0 ...

Page 45

INSTRUCTIONS Legend ASR : Address stack register pointed to by the stack pointer addr : Program memory address (11 bits, high-order two bits are always set to 0) CMP: Compare flag CY : Carry flag h : Halt release ...

Page 46

Instruction Mne- Operand set monic Add ADD r,m (r) (r) + (m) (m) ( m,#n4 (r) ( r,m ADDC (m) ( m,#n4 r,m Subtract SUB (r) (r) – (m) m,#n4 ...

Page 47

ASSEMBLER (AS17K) BUILT-IN MACRO INSTRUCTIONS Legend flag n : FLG symbol < > : Characters enclosed in < > can be omitted. Operand Mnemonic flag 1, ... flag n SKTn flag 1, ... flag n SKFn flag 1, ... ...

Page 48

ELECTRICAL CHARACTERISTICS ABSOLUTE MAXIMUM RATINGS (T A Parameter Symbol V Supply voltage DD V Input voltage P0C, P0D, RESET I P0B Output voltage V P0C, P0D O P0B I High-level output current Each of P0C and P0D OH Total ...

Page 49

DC CHARACTERISTICS (T = -40 to +110 ˚ Symbol Parameter High-level input voltage V P0C, P0D IH1 V RESET IH2 V P0B IH3 V IH4 Low-level input voltage V P0C, P0D IL1 V RESET IL2 V P0B IL3 ...

Page 50

CHARACTERISTICS OF DATA MEMORY FOR HOLDING DATA ON LOW SUPPLY VOLTAGE IN THE STOP MODE (T = –40 to +110 ˚C) A Symbol Parameter Data hold supply volt- V DDDR age Data hold supply 2.0 V DDDR ...

Page 51

SYSTEM CLOCK OSCILLATOR CHARACTERISTICS (T Symbol Parameter System clock oscilla 4 tion frequency V = 2 2 Caution The ...

Page 52

CHARACTERISTIC CURVES (REFERENCE) f vs. V for Operation Guarantee Range –40 to +110 ˚C) A 1300 1000 500 380 300 Operation guarantee range 100 OSC OSC ...

Page 53

I vs 25˚C) A 1000 operation 500 HALT R = 100 k operation R = 100 k HALT R = 330 k operation 100 R = 330 ...

Page 54

PACKAGE DRAWINGS PACKAGE DRAWINGS OF MASS-PRODUCED PRODUCTS (1/2) 16 PIN PLASTIC DIP (300 mil NOTES 1) Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material ...

Page 55

PACKAGE DRAWINGS OF MASS-PRODUCED PRODUCTS (2/2) 16 PIN PLASTIC SOP (300 mil NOTE Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition. Caution The ES ...

Page 56

ES PACKAGE DRAWINGS (1/2) 16 PIN PLASTIC SOP (300 mil) (UNIT: mm 1.91 0.33 56 20.32 17.78 0.89 2.54 PD17107(A1) 7.62 0.254 ...

Page 57

ES PACKAGE DRAWINGS (2/2) 16 PIN CERAMIC SOP (FOR ES ITEM PD17107(A1) T MILLIMETERS INCHES 10.16 0.40 1.02 MAX. ...

Page 58

RECOMMENDED SOLDERING CONDITIONS The conditions listed below shall be met when soldering the PD17107(A1). For details of the recommended soldering conditions, refer to our document SMD Surface Mount Technology Manual (IEI-1207). Please consult with our sales offices in case ...

Page 59

APPENDIX DEVELOPMENT TOOLS The following support tools are available for developing programs for the PD17107(A1). Hardware Name In-circuit emulator The IE-17K, IE-17K-ET, and EMU-17K are in-circuit emulators applicable to the 17K series. IE-17K The IE-17K and IE-17K-ET are connected to ...

Page 60

Software Name Description 17K series AS17K is an assembler assembler applicable to the 17K series. (AS17K) In developing PD17107(A1) programs, AS17K is used in combination with a device file (AS17103). Device file AS17103 contains a device file (AS17103) for the ...

Page 61

Cautions on CMOS Devices 1 Countermeasures against static electricity for all MOSs Caution When handling MOS devices, take care so that they are not electrostatically charged. Strong static electricity may cause dielectric breakdown in gates. When transporting or storing MOS ...

Page 62

SIMPLEHOST is a registered trademark of NEC Corporation. MS-DOS and Windows are trademarks of Microsoft Corporation. PC/AT and PC DOS are trademarks of IBM Corporation. The export of this product from Japan is regulated by the Japanese government. To export ...