AT89C51RC-33AC ATMEL Corporation, AT89C51RC-33AC Datasheet - Page 10

AT89C51RC-33AC

Manufacturer Part Number

AT89C51RC-33AC

Description

8-bit Microcontroller with 32K Bytes Flash

Manufacturer

ATMEL Corporation

Datasheet

1.AT89C51RC-33AC.pdf

(37 pages)

10

AT89C51RC

accesses the SFR at location 0S0H (which is P2). Instructions that use indirect address-

ing access the Upper 128 bytes of data RAM. For example:

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2

(whose address is 0A0H).

Note that stack operations are examples of indirect addressing, so the upper 128 bytes

of data RAM are available as stack space.

The 256 bytes of ERAM can be accessed by indirect addressing, with EXTRAM bit

cleared and MOVX instructions. This part of memory is physically located on-chip, logi-

cally occupying the first 256 bytes of external data memory.

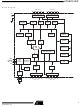

Figure 1. Internal and External Data Memory Address

With EXTRAM = 0, the ERAM is indirectly addressed, using the MOVX instruction in

combination with any of the registers R0, R1 of the selected bank or DPTR. An access

to ERAM will not affect ports P0, P2, P3.6 (WR), and P3.7 (RD). For example, with

EXTRAM = 0,

where R0 contains 0A0H, accesses the ERAM at address 0A0H rather than external

memory. An access to external data memory locations higher than FFH (i.e. 0100H to

FFFFH) will be performed with the MOVX DPTR instructions in the same way as in the

standard 80C51, i.e., with P0 and P2 as data/address bus, and P3.6 and P3.7 as write

and read timing signals. Refer to Figure 1.

With EXTRAM = 1, MOVX @ Ri and MOVX@DPTR will be similar to the standard

80C51. MOVX@Ri will provide an 8-bit address multiplexed with data on Port 0 and any

output port pins can be used to output higher-order address bits. This is to provide the

external paging capability. MOVX@DPTR will generate a 16-bit address. Port 2 outputs

the high-order 8 address bits (the contents of DP0H), while Port 0 multiplexes the low-

order 8 address bits (the contents of DP0L) with data. MOVX@Ri and MOVX@DPTR

will generate either read or write signals on P3.6 (WR) and P3.7 (RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and

upper RAM) internal data memory. The stack may not be located in the ERAM.

MOV@R0, # data

MOVX@R0, # data

(with EXTRAM = 0)

FF

00

ERAM

256 BYTES

FF

80

00

UPPER

128 BYTES

INTERNAL

RAM

LOWER

128 BYTES

INTERNAL

RAM

FF

80

SPECIAL

FUNCTION

REGISTER

FFFF

0100

0000

EXTERNAL

DATA

MEMORY

1920B–MICRO–11/02