HYS64V16220GU-10 SIEMENS [Siemens Semiconductor Group], HYS64V16220GU-10 Datasheet

HYS64V16220GU-10

Related parts for HYS64V16220GU-10

HYS64V16220GU-10 Summary of contents

Page 1

... PC main memory applications 1 bank 8M 64 and 2 bank 16M • Optimized for byte-write non-parity or ECC applications • JEDEC standard Synchronous DRAMs (SDRAM) • Fully PC board layout compatible to INTEL’s Rev. 1.0 module specification • SDRAM Performance • f Clock frequency (max Clock access time ...

Page 2

... Synchronous DRAMs (SDRAMs) for non-parity and ECC applications. The DIMMs use -8 and -8B speed sort 8M 8 SDRAM devices in TSOP-54 packages to meet the PC100 requirement. Modules which use -10 parts are suitable for PC66 applications only. Decoupling capacitors are mounted on the PC board. The PC board design is according to INTEL’ ...

Page 3

... Power (+ 3.3 Volt Ground SS SCL Clock for Presence Detect SDA Serial Data Out for Presence Detect N.C. No Connection Rows Columns Bank Select SDRAM Modules Refresh Period Interval 15.6 s 1998-08-01 ...

Page 4

... A5 120 CLK2 121 A9 NC 122 BA0 WP 123 A11 SDA 124 V CC SCL 125 CLK1 V 126 SDRAM Modules PIN # Symbol 127 V SS 128 CKE0 129 CS3 130 DQMB6 131 DQMB7 132 NC 133 V CC 134 NC 135 NC 136 CB6 137 CB7 ...

Page 5

... DQ0-DQ7 A0-A11, BA0, BA1 D0-D7, (D8) V D0-D7, (D8) CC C0-C15, (C16, C17) V D0-D7, (D8) SS RAS D0-D7, (D8) CAS D0-D7, (D8) CKE0 D0-D7, (D8) Note only used in the x72 ECC version. Block Diagram for 8M 64/72 SDRAM DIMM Modules (HYS 64/72V8200GU) Semiconductor Group HYS 64(72)V8200/16220GU-8/-10 DQMB4 DQ(39:32) D0 DQMB5 DQ(47:40 DQMB6 DQ(55:48) D2 DQMB7 DQ(63:56) D3 CLK0 CLK1 CLK2 ...

Page 6

... D0-D15, (D16, D17) CKE0 D0-D7, (D16 CKE1 D9-D15, (D17) Note: D16 & D17 is only used in the x72 ECC version and all resistor values are 10 Block Diagram for 16M 64/72 SDRAM DIMM Modules (HYS 64/72V1620GU) Semiconductor Group HYS 64(72)V8200/16220GU-8/-10 CS DQM DQMB4 DQ0-DQ7 DQ(39:32 ...

Page 7

... MHz Symbol max ICL SDRAM Modules Symbol Limit Values min. max – 0.5 0 2.4 – – 0 – I(L) I – O(L) Limit Values max. ...

Page 8

... CC2PS min. CK CC2N infinity CK CC2NS V I CKE IH(MIN.) CC3N V I CKE IL(MAX.) CC3P – I CC4 – I CC5 I standard version CC6 8 SDRAM Modules -8/-8B -10 Unit Note max. 1 110 ...

Page 9

... – 20 RCD t 20 – 100k 60 RAS t 70 – – 20 RRD t 1 – 1 CCD 9 SDRAM Modules Unit -8B -10 PC66 – 10 – ns – 15 – ns 100 – 100 MHz 83 – 66 MHz 6 – – – 3.5 – ns – ...

Page 10

... – – 2 – DQZ t 2 – 2 DPL t 5 – 5 DAL t 0 – 0 DQW 10 SDRAM Modules Unit -8B -10 PC66 64 – – 10 – ns – 3 – ns – 0 – – 2 CLK – 2 – CLK – ...

Page 11

... The specified values are valid when addresses are changed no more than once during and when No Operation commands are registered on every rising clock edge during Values are shown per module bank. 2. The specified values are valid when data inputs (DQ’s) are stable during 3 ...

Page 12

... A serial presence detect storage device - E about the module configuration, speed, etc. is written into the E production using a serial presence detect protocol (I SPD-Table for PC100 Modules Byte# Description 0 Number of SPD bytes 1 Total bytes in Serial PD 2 Memory Type 3 Number of Row Addresses (without BS bits) 4 Number of Column ...

Page 13

... SPD-Table for PC100 Modules (cont’d) Byte# Description 15 Minimum clock delay for back-to- back random column address 16 Burst Length supported 17 Number of SDRAM banks 18 Supported CAS Latencies 19 CS Latencies 20 WE Latencies 21 SDRAM DIMM module attributes 22 SDRAM Device Attributes: General 23 Min. Clock Cycle ...

Page 14

... SPD-Table for PC100 Modules (cont’d) Byte# Description 29 Minimum RAS to t CAS delay RCD 30 Minimum RAS pulse width t RAS 31 Module Bank Density (per bank) 32 SDRAM input setup time 33 SDRAM input hold time 34 SDRAM data input hold time 35 SDRAM data input setup time ...

Page 15

... SPD-Table for PC66 Modules Byte# Description 0 Number of SPD bytes 1 Total bytes in Serial PD 2 Memory Type 3 Number of Row Addresses (without BS bits) 4 Number of Column Addresses (for x8 SDRAM) 5 Number of DIMM Banks 6 Module Data Width 7 Module Data Width (cont’d) 8 Module Interface Levels 9 SDRAM Cycle Time at ...

Page 16

... SPD-Table for PC66 Modules (cont’d) Byte# Description 22 SDRAM Device Attributes: General 23 Min. Clock Cycle Time at CAS Latency = 2 24 Max. data access time from Clock for CL Minimum Clock Cycle Time Maximum Data Access Time from Clock ...

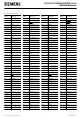

Page 17

... Package outlines for tubes, trays etc. are contained in our Data Book “Package Information”. SMD = Surface Mounted Device Semiconductor Group HYS 64(72)V8200/16220GU-8/-10 133.35 127. 6.35 42. 1.27 = 115.57 124 125 *) 17 SDRAM Modules 4 84 1.27 ± 0.1 168 2. ECC modules only GLD09159 Dimensions in mm 1998-08-01 ...