MAX1304ECM-T Maxim Integrated, MAX1304ECM-T Datasheet - Page 22

MAX1304ECM-T

Manufacturer Part Number

MAX1304ECM-T

Description

Analog to Digital Converters - ADC

Manufacturer

Maxim Integrated

Datasheet

1.MAX1306ECM-T.pdf

(37 pages)

Specifications of MAX1304ECM-T

Number Of Channels

8

Architecture

SAR

Conversion Rate

1075 KSPs

Resolution

12 bit

Input Type

Single-Ended

Snr

71 dB

Interface Type

Parallel

Operating Supply Voltage

2.7 V to 5.25 V, 4.75 V to 5.25 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Package / Case

LQFP-48

Maximum Power Dissipation

1818.2 mW

Minimum Operating Temperature

- 40 C

Number Of Converters

1

Voltage Reference

2.5 V

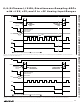

To start a conversion using internal clock mode, pull

CONVST low for the acquisition time (t

acquires the signal while CONVST is low, and conver-

sion begins on the rising edge of CONVST. The end-of-

conversion signal (EOC) pulses low whenever a

conversion result becomes available for read. The end-

of-last-conversion signal (EOLC) goes low when the last

conversion result is available (Figure 7).

To start a conversion using external clock mode, pull

CONVST low for the acquisition time (t

acquires the signal while CONVST is low. The rising

edge of CONVST is the sampling instant. Apply an

external clock to CLK to start the conversion. To avoid

T/H droop degrading the sampled analog input signals,

8-/4-/2-Channel, 12-Bit, Simultaneous-Sampling ADCs

with ±10V, ±5V, and 0 to +5V Analog Input Ranges

Figure 7. Read During Conversion—Channel 0 and Channel 1 Selected, Internal Clock

22

CONVST

D0–D11

EOLC

______________________________________________________________________________________

EOC

CS*

RD

*CS CAN BE LOW AT ALL TIMES, LOW DURING THE RD CYCLES, OR THE SAME AS RD.

TRACK

t

ACQ

INSTANT

SAMPLE

Starting a Conversion

ACQ

ACQ

t

CONV

). The T/H

). The T/H

t

CTR

t

ACC

t

the first CLK pulse must occur within 10µs from the

rising edge of CONVST. Additionally, the external clock

frequency must be greater than 100kHz to avoid T/H

droop-degrading accuracy. The first conversion result

is available for read when EOC goes low on the rising

edge of the 13th clock cycle. Subsequent conversion

results are available after every third clock cycle there-

after (Figures 8 and 9).

In both internal and external clock modes, hold

CONVST high until the last conversion result is read. If

CONVST goes low in the middle of a conversion, the

current conversion is aborted and a new conversion is

initiated. Furthermore, there must be a period of bus

inactivity (t

edge of CONVST for the specified ADC performance.

REQ

HOLD

t

EOC

CH0

t

QUIET

NEXT

t

RDH

) for 50ns or longer before the falling

t

RDL

CH1

t

t

CVEOLCD

QUIET

t

RTC

≥ 50ns

TRACK