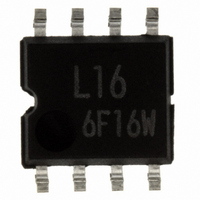

BR24L16F-WE2 Rohm Semiconductor, BR24L16F-WE2 Datasheet - Page 7

BR24L16F-WE2

Manufacturer Part Number

BR24L16F-WE2

Description

IC EEPROM 16KBIT 400KHZ 8SOP

Manufacturer

Rohm Semiconductor

Datasheet

1.BR24L08F-WE2.pdf

(33 pages)

Specifications of BR24L16F-WE2

Memory Size

16K (2K x 8)

Format - Memory

EEPROMs - Serial

Memory Type

EEPROM

Speed

400kHz

Interface

I²C, 2-Wire Serial

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOP

Clock Frequency

400kHz

Supply Voltage Range

1.8V To 5.5V

Memory Case Style

SOP

No. Of Pins

8

Operating Temperature Range

-40°C To +85°C

Svhc

No SVHC (18-Jun-2010)

Package /

RoHS Compliant

Memory Configuration

2K X 8

Interface Type

I2C, Serial

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

BR24L16F-WE2TR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

BR24L16F-WE2

Manufacturer:

ROHM/罗姆

Quantity:

20 000

●I

2

○I

○Start condition (Start bit recognition)

○Stop condition (stop bit recongnition)

○Acknowledge (ACK) signal

○Device addressing

C BUS communication

・Before executing each command, start condition (start bit) where SDA goes from

・This IC always detects whether SDA and SCL are in start condition (start bit) or not, therefore, unless this confdition is

・Each command can be ended by SDA rising from

・This acknowledge (ACK) signal is a software rule to show whether data transfer has been made normally or not. In master

・The device (this IC at slave address input of write command, read command, and μ-COM at data output of read

・This IC, after recognizing start condition and slave address (8bit), outputs acknowledge signal (ACK signal)

・Each write action outputs acknowledge signal (ACK signal)

・Each read action outputs 8bit data (read data), and detects acknowledge signal (ACK signal) 'LOW'.

・When acknowledge signal (ACK signal) is detected, and stop condition is not sent from the master (μ-COM) side, this IC

・Output slave address after start condition from master.

・The significant 4 bits of slave address are used for recognizing a device type. The device code of this IC is fixed to

・Next slave addresses (A2 A1 A0 --- device address) are for selecting devices, and plural ones can be used on a same bus

・The most insignificant bit (R/W --- READ / WRITE) of slave address is used for designating write or read action, and is as

I

acknowledge is always required after each byte. I

communication lines of serial data (SDA) and serial clock (SCL).

Among devices, there are “master” that generates clock and control communication start and end, and “slave” that is

controlled by address peculiar to devices. EEPROM becomes “slave”. And the device that outputs data to bus during data

communication is called “transmitter”, and the device that receives data is called “receiver”.

2

2

Note) Up to 4 units BR24L04-W, up to 2 units of BR24L08-W, and one unit of BR24L16-W can be connected.

and slave, the device (μ-COM at slave address input of write command, read command, and this IC at data output of read

command) at the transmitter (sending) side releases the bus after output of 8bit data.

command) at the receiver (receiving) side sets SDA

signal) showing that it has received the 8bit data.

continues data output. When acknowledge signal (ACK signal) is not detected, this IC stops data transfer, and recognizes

stop cindition (stop bit), and ends read action. And this IC gets in status.

according to the number of device addresses.

shown below.

C BUS data communication

C BUS data communication starts by start condition input, and ends by stop condition input. Data is always 8bit long, and

'

satisfied, any command is executed.

PS, P0~P2 are page select bits.

HIGH

BR24L01A-W

BR24L02-W

BR24L04-W

BR24L08-W

BR24L16-W

BR24L32-W

BR24L64-W

Device address is set by 'H' and 'L' of each pin of A0, A1, and A2.

'

Type

is necessary.

Setting R / W to 0 ------- write (setting 0 to word address setting of random read)

Setting R / W to 1 ------- read

1

1

1

1

1

1

1

SDA

SCL

0

0

0

0

0

0

0

1

1

1

1

1

1

1

START

condition

S

0

0

0

0

0

0

0

ADDRESS

Slave address

A2

A2

A2

A2

P2

A2

A2

1-7

A1

A1

A1

P1

P1

A1

A1

R/W

8

Fig.35 Data transfer timing

ACK

9

A0

A0

PS

P0

P0

A0

A0

2

C BUS carries out data transmission with plural devices connected by 2

'

LOW

1-7

R/W

R/W

R/W

R/W

R/W

R/W

R/W

DATA

'

LOW

7/32

'

to

8

Maximum number of

'

'

'

HIGH

connected buses

during 9 clock cycles, and outputs acknowledge signal (ACK

LOW

ACK

9

'

'

, at receiving 8bit data (word address and write data).

8

8

4

2

1

8

8

when stop condition (stop bit), namely, SCL is

1-7

DATA

8

ACK

9

condition

'

STOP

HIGH

GND

P

A0

A1

A2

'

1

2

3

4

down to

BR24L01A-W

BR24L02-W

BR24L04-W

BR24L08-W

BR24L16-W

BR24L32-W

BR24L64-W

'

LOW

'

'

when SCL is

LOW

8

7

5

6

Vcc

WP

SCL

SDA

'

'

HIGH

.

'

1010

'

'

.