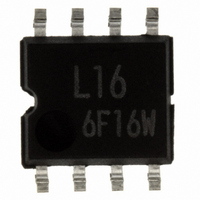

BR24L16F-WE2 Rohm Semiconductor, BR24L16F-WE2 Datasheet - Page 9

BR24L16F-WE2

Manufacturer Part Number

BR24L16F-WE2

Description

IC EEPROM 16KBIT 400KHZ 8SOP

Manufacturer

Rohm Semiconductor

Datasheet

1.BR24L08F-WE2.pdf

(33 pages)

Specifications of BR24L16F-WE2

Memory Size

16K (2K x 8)

Format - Memory

EEPROMs - Serial

Memory Type

EEPROM

Speed

400kHz

Interface

I²C, 2-Wire Serial

Voltage - Supply

1.8 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Package / Case

8-SOP

Clock Frequency

400kHz

Supply Voltage Range

1.8V To 5.5V

Memory Case Style

SOP

No. Of Pins

8

Operating Temperature Range

-40°C To +85°C

Svhc

No SVHC (18-Jun-2010)

Package /

RoHS Compliant

Memory Configuration

2K X 8

Interface Type

I2C, Serial

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

BR24L16F-WE2TR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

BR24L16F-WE2

Manufacturer:

ROHM/罗姆

Quantity:

20 000

○Notes on write cycle continuous input

○Notes on page write cycle

○Write protect (WP) terminal

List of numbers of page write

In the case BR24L02-W, 1 page=8bytes, but the page

write cycle write time is 5ms at maximum for 8byte bulk write.

It does not stand 5ms at maximum × 8byte=40ms(Max.).

The above numbers are maximum bytes for respective types.

Any bytes below these can be written.

Number of

・Write protect (WP) function

Product

number

SDA

LINE

Pages

When WP terminal is set Vcc (H level), data rewrite of all addresses is prohibited. When it is set GND (L level), data rewrite

of all address is enabled. Be sure to connect this terminal to Vcc or GND, or control it to H level or L level. Do not use it

open.

At extremely low voltage at power ON / OFF, by setting the WP terminal 'H', mistake write can be prevented.

During tWR, set the WP terminal always to 'L'. If it is set 'H', write is forcibly terminated.

Note)

Fig.42 Difference of each type of slave address

A

R

S

T

T

1 0

ADDRESS

1 0

BR24L01A-W

Note)

BR24L02-W

SLAVE

1

0

8Byte

A2

1

A1

A0

0

W

R

/

W

R

T

*1 *2 *3

E

A 2

I

A

C

K

Fig.41 Page write cycle

WA

*1

7

A 1

ADDRESS(n)

BR24L04-W

BR24L08-W

BR24L16-W

A 0

WORD

16Byte

WA

0

A

C

K

D7

BR24L32-W

BR24L64-W

DATA(n)

32Byte

D0

C

A

K

9/32

*1 BR24L01A-W becomes Don’t care.

*2 BR24L04-W, BR24L08-W, and BR24L16-W become (n+15).

*3 BR24L32-W and BR24L64-W become (n+31).

DATA(n+7)

*1 In BR24L16-W, A2 becomes P2.

*2 In BR24L08-W, BR24L16-W, A1 becomes P1.

*3 In BR24L04-W, A0 becomes PS, and in BR24L08-W and

06h

in BR24L16-W, A0 becomes P0.

○Internal address increment

Page write mode (in the case of BR24L02-W)

For example, when it is started from address 06h,

therefore, increment is made as below,

06h → 07h → 00h → 01h ---, which please note.

*

*2

*3

WA7 ----- WA4 WA3

D0

0

0

0

0

0

0

binary number.

06h・・・06 in hexadecimal, therefore, 00000110 becomes a

A

C

K

S

T

O

P

-----

-----

-----

-----

-----

-----

At STOP (stop bit),

write starts.

tWR(maximum : 5ms)

Command is not accepted for this period.

S

T

A

R

T

Next command

Significant bit is fixed.

No digit up

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

WA2 WA1 WA0

0

0

0

1

1

0

0

0

1

1

1

0

0

1

0

0

1

0

Increment