STEVAL-IFP007V1 STMicroelectronics, STEVAL-IFP007V1 Datasheet - Page 24

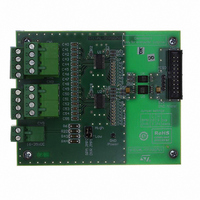

STEVAL-IFP007V1

Manufacturer Part Number

STEVAL-IFP007V1

Description

BOARD EVAL BASED ON SCLT3-8

Manufacturer

STMicroelectronics

Specifications of STEVAL-IFP007V1

Main Purpose

Interface, Digital Signal Termination

Embedded

No

Utilized Ic / Part

SCLT3-8

Primary Attributes

8 Channel Optical Isolation

Secondary Attributes

SPI Interface

Processor To Be Evaluated

SCLT3

Data Bus Width

16 bit

Interface Type

SPI

Operating Supply Voltage

24 V

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

497-9045

Application considerations

3

3.1

24/33

Application considerations

SCLT serial link configurations

As long as /CS is low, a slave is able to transmit data bits whatever the length of the data

frames. This feature allows several SCLT circuits to be connected in a daisy chain

configuration.

In the daisy chain configuration with several SCLT circuits (N) all the circuits are addressed

by the same chip select and receive the clock signals from the same clock. They all work

synchronously.

The SPI output MISO of the previous SCLT

the next SCLT

input of the master. The MOSI of the first SCLT

So, the SPI master reads the whole chain of N 16-bit words starting with the word of the last

SCLT

Detailed considerations on SPI operation and daisy chain configurations are also described

in ST application notes AN2846 and AN2853.

Figure 17. SCLT connection to opto-couplers, bus controller SPI master, and output

The configuration of the SCLT slave bus circuit allows the master bus controller to operate

with other slave circuits in a different phase and polarity mode as long as it runs

communication with SCLT in C

The requirement to transfer data in a daisy chain configuration is to use an SPI control

master circuit that is able to send and receive a bit stream from 8 minimum up to 128 within

one chip select sequence depending on the number of SCLTs and SPI mode (8- or 16-bit).

N

and ending with the word of the first SCLT

SPI master

driver

MISO

MISO

MISO

MOSI

MOSI

MOSI

P

SCK

SCK

SCK

/CS

/CS

/CS

device and the output MISO of the last SCLT

Case 1: 16-DI

SCK

SCK

MISO

MISO

MOSI

MOSI

/CS

/CS

SCK

SCK

MISO

MISO

MOSI

MOSI

/CS

/CS

Doc ID 15191 Rev 3

PHA

SCLT

SCLT

= 0 and C

2

1

= 1Mbps coupler

P-1

POL

device is connected to the SPI input MOSI of

1

can be kept open or grounded.

= 0.

1

SPI master

.

MISO

MISO

MOSI

MOSI

SCK

SCK

/CS

/CS

/CS

/CS

Case 2: 8-DI and 8-DO

1

1

2

2

N

is connected to the MISO

SCK

SCK

SCK

MISO

MISO

MISO

/CS

/CS

/CS

SCK

SCK

SCK

SDI

SDI

SDI

SDO

SDO

SDO

/CS

/CS

/CS

SCLT

VNI8200XP

SCLT3-8BT8