ATTINY461-20MU Atmel, ATTINY461-20MU Datasheet - Page 88

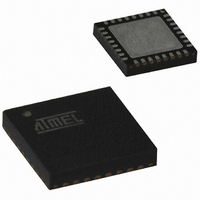

ATTINY461-20MU

Manufacturer Part Number

ATTINY461-20MU

Description

IC AVR MCU 4K 20MHZ 32-QFN

Manufacturer

Atmel

Series

AVR® ATtinyr

Specifications of ATTINY461-20MU

Core Processor

AVR

Core Size

8-Bit

Speed

20MHz

Connectivity

USI

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

16

Program Memory Size

4KB (2K x 16)

Program Memory Type

FLASH

Eeprom Size

256 x 8

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 11x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

32-VQFN Exposed Pad, 32-HVQFN, 32-SQFN, 32-DHVQFN

Processor Series

ATTINY4x

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

256 B

Interface Type

2-Wire, SPI, USI

Maximum Clock Frequency

20 MHz

Number Of Programmable I/os

16

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 11 Channel

For Use With

ATSTK600-DIP40 - STK600 SOCKET/ADAPTER 40-PDIPATAVRBC100 - REF DESIGN KIT BATTERY CHARGER770-1007 - ISP 4PORT ATMEL AVR MCU SPI/JTAG

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATTINY461-20MU

Manufacturer:

KODENSHI

Quantity:

991

Company:

Part Number:

ATTINY461-20MUR

Manufacturer:

ATMEL

Quantity:

5 560

- Current page: 88 of 242

- Download datasheet (5Mb)

• Bit 1 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware

when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by

writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt

Enable), and TOV0 are set, the Timer/Counter0 Overflow interrupt is executed.

• Bit 0 – ICF0: Timer/Counter0, Input Capture Flag

This flag is set when a capture event occurs on the ICP0 pin. When the Input Capture Register

(ICR0) is set to be used as the TOP value, the ICF0 flag is set when the counter reaches the

TOP value.

ICF0 is automatically cleared when the Input Capture Interrupt Vector is executed. Alternatively,

ICF0 can be cleared by writing a logic one to its bit location.

ATtiny261/461/861

88

2588E–AVR–08/10

Related parts for ATTINY461-20MU

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel Corporation

Datasheet:

Part Number:

Description:

IC MCU AVR 4K FLASH 20MHZ 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4K FLASH 15MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4KB FLASH 15MHZ 32-VQFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 4KB FLASH 20MHZ 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC MCU AVR 4K 20MHZ 32QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Microcontrollers (MCU) 4kB Flash 0.256kB EEPROM 16 I/O Pins

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 2K FLASH, 20SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

IC, MCU, 8BIT, 2K FLASH, 20PDIP

Manufacturer:

Atmel

Datasheet: