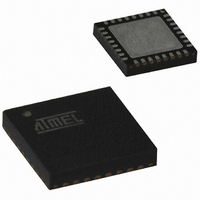

AT90PWM3-16MQ Atmel, AT90PWM3-16MQ Datasheet - Page 195

AT90PWM3-16MQ

Manufacturer Part Number

AT90PWM3-16MQ

Description

IC AVR MCU FLASH 8K 32QFN

Manufacturer

Atmel

Series

AVR® 90PWM Lightingr

Datasheet

1.AT90PWM3B-16SU.pdf

(361 pages)

Specifications of AT90PWM3-16MQ

Core Processor

AVR

Core Size

8-Bit

Speed

16MHz

Connectivity

SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

27

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 11x10b; D/A 1x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 105°C

Package / Case

32-QFN

Processor Series

AT90PWMx

Core

AVR8

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI, USART

Maximum Clock Frequency

16 MHz

Number Of Programmable I/os

27

Number Of Timers

2

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 105 C

Mounting Style

SMD/SMT

3rd Party Development Tools

EWAVR, EWAVR-BL

Development Tools By Supplier

ATAVRDRAGON, ATSTK500, ATSTK600, ATAVRISP2, ATAVRONEKIT, ATAVRFBKIT, ATAVRISP2

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 11 Channel

On-chip Dac

10 bit, 1 Channel

For Use With

ATSTK600-SOIC - STK600 SOCKET/ADAPTER FOR SOICATAVRMC200 - KIT EVAL FOR AT90PWM3 ASYNCATAVRFBKIT - KIT DEMO BALLAST FOR AT90PWM2ATAVRISP2 - PROGRAMMER AVR IN SYSTEMATSTK520 - ADAPTER KIT FOR 90PWM

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

AT90PWM3-16MQT

Manufacturer:

Atmel

Quantity:

1 325

- Current page: 195 of 361

- Download datasheet (7Mb)

18.7.3

18.7.4

4317J–AVR–08/10

Receive Complete Flag and Interrupt

Receiver Error Flags

The receive function example reads all the I/O Registers into the Register File before any com-

putation is done. This gives an optimal receive buffer utilization since the buffer location read will

be free to accept new data as early as possible.

The USART Receiver has one flag that indicates the Receiver state.

The Receive Complete (RXC) flag indicates if there are unread data present in the receive buf-

fer. This flag is one when unread data exist in the receive buffer, and zero when the receive

buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled (RXEN = 0),

the receive buffer will be flushed and consequently the RXC bit will become zero.

When the Receive Complete Interrupt Enable (RXCIE) in UCSRB is set, the USART Receive

Complete interrupt will be executed as long as the RXC flag is set (provided that global inter-

rupts are enabled). When interrupt-driven data reception is used, the receive complete routine

must read the received data from UDR in order to clear the RXC flag, otherwise a new interrupt

will occur once the interrupt routine terminates.

The USART Receiver has three error flags: Frame Error (FE), Data OverRun (DOR) and Parity

Error (UPE). All can be accessed by reading UCSRA. Common for the error flags is that they are

located in the receive buffer together with the frame for which they indicate the error status. Due

to the buffering of the error flags, the UCSRA must be read before the receive buffer (UDR),

since reading the UDR I/O location changes the buffer read location. Another equality for the

error flags is that they can not be altered by software doing a write to the flag location. However,

all flags must be set to zero when the UCSRA is written for upward compatibility of future

USART implementations. None of the error flags can generate interrupts.

The Frame Error (FE) flag indicates the state of the first stop bit of the next readable frame

stored in the receive buffer. The FE flag is zero when the stop bit was correctly read (as one),

and the FE flag will be one when the stop bit was incorrect (zero). This flag can be used for

detecting out-of-sync conditions, detecting break conditions and protocol handling. The FE flag

is not affected by the setting of the USBS bit in UCSRC since the Receiver ignores all, except for

the first, stop bits. For compatibility with future devices, always set this bit to zero when writing to

UCSRA.

The Data OverRun (DOR) flag indicates data loss due to a receiver buffer full condition. A Data

OverRun occurs when the receive buffer is full (two characters), it is a new character waiting in

the Receive Shift Register, and a new start bit is detected. If the DOR flag is set there was one

or more serial frame lost between the frame last read from UDR, and the next frame read from

UDR. For compatibility with future devices, always write this bit to zero when writing to UCSRA.

The DOR flag is cleared when the frame received was successfully moved from the Shift Regis-

ter to the receive buffer.

The following example (See Figure 18-5.) represents a Data OverRun condition. As the receive

buffer is full with CH1 and CH2, CH3 is lost. When a Data OverRun condition is detected, the

OverRun error is memorized. When the two characters CH1 and CH2 are read from the receive

buffer, the DOR bit is set (and not before) and RxC remains set to warn the application about the

overrun error.

AT90PWM2/3/2B/3B

195

Related parts for AT90PWM3-16MQ

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC AVR MCU FLASH 8K 32SOIC

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU AVR 8K FLASH 16MHZ 32-QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

DEV KIT FOR AVR/AVR32

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Monolithic Integrated Feature Phone Circuit

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Multistandard Video-IF and Quasi Parallel Sound Processing

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

High-performance EE PLD

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

8-bit Flash Microcontroller

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

2-Wire Serial EEPROM

Manufacturer:

ATMEL Corporation

Datasheet: