ATMEGA8535L-8MI Atmel, ATMEGA8535L-8MI Datasheet - Page 160

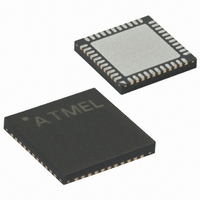

ATMEGA8535L-8MI

Manufacturer Part Number

ATMEGA8535L-8MI

Description

IC AVR MCU 8K LV 8MHZ IND 44-QFN

Manufacturer

Atmel

Series

AVR® ATmegar

Specifications of ATMEGA8535L-8MI

Core Processor

AVR

Core Size

8-Bit

Speed

8MHz

Connectivity

I²C, SPI, UART/USART

Peripherals

Brown-out Detect/Reset, POR, PWM, WDT

Number Of I /o

32

Program Memory Size

8KB (4K x 16)

Program Memory Type

FLASH

Eeprom Size

512 x 8

Ram Size

512 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 8x10b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

44-VQFN Exposed Pad

Data Bus Width

8 bit

Data Ram Size

512 B

Interface Type

SPI, TWI, UART

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

32

Number Of Timers

3

Operating Supply Voltage

2.7 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Minimum Operating Temperature

- 40 C

On-chip Adc

10 bit, 8 Channel

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ATMEGA8535L-8MI

Manufacturer:

SanRex

Quantity:

1 000

- Current page: 160 of 321

- Download datasheet (3Mb)

Asynchronous Operational

Range

160

ATmega8535(L)

Figure 75. Stop Bit Sampling and Next Start Bit Sampling

The same majority voting is done to the stop bit as done for the other bits in the frame. If

the stop bit is registered to have a logic 0 value, the Frame Error (FE) Flag will be set.

A new high to low transition indicating the start bit of a new frame can come right after

the last of the bits used for majority voting. For Normal Speed mode, the first low level

sample can be at point marked (A) in Figure 75. For Double Speed mode the first low

level must be delayed to (B). (C) marks a stop bit of full length. The early start bit detec-

tion influences the operational range of the Receiver.

The operational range of the Receiver is dependent on the mismatch between the

received bit rate and the internally generated baud rate. If the Transmitter is sending

frames at too fast or too slow bit rates, or the internally generated baud rate of the

Receiver does not have a similar (see Table 62) base frequency, the Receiver will not

be able to synchronize the frames to the start bit.

The following equations can be used to calculate the ratio of the incoming data rate and

internal receiver baud rate.

D

S

S

S

R

Table 62 and Table 63 list the maximum receiver baud rate error that can be tolerated.

Note that normal speed mode has higher toleration of baud rate variations.

F

M

slow

(U2X = 0)

(U2X = 1)

Sample

Sample

RxD

Sum of character size and parity size (D = 5 to 10 bit).

Samples per bit. S = 16 for Normal Speed mode and S = 8 for Double Speed

mode.

First sample number used for majority voting. S

for Double Speed mode.

Middle sample number used for majority voting. S

S

is the ratio of the slowest incoming data rate that can be accepted in relation to the

receiver baud rate. R

accepted in relation to the Receiver baud rate.

M

R

= 5 for Double Speed mode.

slow

=

------------------------------------------ -

S 1

1

1

–

(

D

2

+

+

D S ⋅

3

2

1

fast

)S

4

+

is the ratio of the fastest incoming data rate that can be

S

F

5

3

6

7

4

8

STOP 1

9

5

10

F

0/1

(A)

6

R

= 8 for Normal Speed and S

M

fast

0/1

= 9 for Normal Speed and

=

(B)

0/1

0/1

-----------------------------------

(

D

(

+

D

1

+

)S

2

)S

+

S

2502K–AVR–10/06

(C)

M

F

= 4

Related parts for ATMEGA8535L-8MI

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

IC AVR MCU 2.4GHZ XCEIVER 64QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA644/AT86RF230 40-DIP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA644P/AT86RF230 QFN

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA644P/AT86RF230 TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA1281/AT86RF230 64-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA1280/AT86RF230 100TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA1280/AT86RF100-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

BUNDLE ATMEGA2560V/AT86RF230-ZU

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

MCU ATMEGA2561/AT86RF230 64-TQFP

Manufacturer:

Atmel

Datasheet:

Part Number:

Description:

INTERVAL AND WIPE/WASH WIPER CONTROL IC WITH DELAY

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

Low-Voltage Voice-Switched IC for Hands-Free Operation

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

MONOLITHIC INTEGRATED FEATUREPHONE CIRCUIT

Manufacturer:

ATMEL Corporation

Datasheet:

Part Number:

Description:

AM-FM Receiver IC U4255BM-M

Manufacturer:

ATMEL Corporation

Datasheet: