CY8C26643-24PI Cypress Semiconductor Corp, CY8C26643-24PI Datasheet - Page 19

CY8C26643-24PI

Manufacturer Part Number

CY8C26643-24PI

Description

IC MCU 16K FLASH 256B 48-DIP

Manufacturer

Cypress Semiconductor Corp

Series

PSOC™ CY8C26xxxr

Datasheet

1.CY8C25122-24PI.pdf

(148 pages)

Specifications of CY8C26643-24PI

Core Processor

M8C

Core Size

8-Bit

Speed

24MHz

Connectivity

SPI, UART/USART

Peripherals

LVD, POR, PWM, WDT

Number Of I /o

44

Program Memory Size

16KB (16K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 5.25 V

Data Converters

A/D 1x8b, 1x11b, 1x12b; D/A 1x9b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

48-DIP (0.600", 15.24mm)

Operating Temperature (min)

-40C

Operating Temperature (max)

85C

Applications

CapSense

Technology

CMOS

Processing Unit

Microcontroller

Operating Supply Voltage (min)

3V

Operating Supply Voltage (typ)

3.3/5V

Operating Supply Voltage (max)

5.25V

Package Type

PDIP

Screening Level

Industrial

Pin Count

48

Mounting

Through Hole

Rad Hardened

No

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Lead Free Status / RoHS Status

Not Compliant, Contains lead / RoHS non-compliant

Other names

428-1432

428-1432-5

428-1432

428-1432-5

428-1432

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C26643-24PI

Manufacturer:

CY

Quantity:

9

2.0

2.1

This family of microcontrollers is based on a high perfor-

mance, 8-bit, Harvard architecture microprocessor. Five

registers control the primary operation of the CPU core.

These registers are affected by various instructions, but

are not directly accessible through the register space by

the user. For more details on addressing with the register

space, see section 4.0.

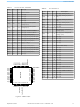

Table 7:

The 16 bit Program Counter Register (CPU_PC) allows

for direct addressing of the full 16 Kbytes of program

memory space available in the largest members of this

family. This forms one contiguous program space, and

no paging is required.

The Accumulator Register (CPU_A) is the general-pur-

pose register that holds the results of instructions that

specify any of the source addressing modes.

The Index Register (CPU_X) holds an offset value that is

used in the indexed addressing modes. Typically, this is

used to address a block of data within the data memory

space.

The Stack Pointer Register (CPU_SP) holds the address

of the current top-of-stack in the data memory space. It is

affected by the PUSH, POP, LCALL, CALL, RETI, and

September 5, 2002

Flags

Program Counter

Accumulator

Stack Pointer

Index

CPU Architecture

Introduction

Register

CPU Registers and Mnemonics

CPU_F

CPU_PC

CPU_A

CPU_SP

CPU_X

Mnemonic

Document #: 38-12010 CY Rev. ** CMS Rev. 3.20

RET instructions, which manage the software stack. It

can also be affected by the SWAP and ADD instructions.

The Flag Register (CPU_F) has three status bits: Zero

Flag bit [1]; Carry Flag bit [2]; Supervisory State bit [3].

The Global Interrupt Enable bit [0] is used to globally

enable or disable interrupts. An extended I/O space

address, bit [4], is used to determine which bank of the

register space is in use. The user cannot manipulate the

Supervisory State status bit [3]. The flags are affected by

arithmetic, logic, and shift operations. The manner in

which each flag is changed is dependent upon the

instruction being executed (i.e., AND, OR, XOR... See

Table 23 on page

25).

CPU Architecture

19