XE1205I074TRLF Semtech, XE1205I074TRLF Datasheet

XE1205I074TRLF

Specifications of XE1205I074TRLF

Related parts for XE1205I074TRLF

XE1205I074TRLF Summary of contents

Page 1

... FEI (Frequency Error Indicator) with built-in AFC • RSSI (Received Signal Strength Indicator) • 16-byte FIFO for transmit / receive data buffering and transfer via SPI bus ORDERING INFORMATION Part number XE1205I074TRLF (1) TR refers to tape & reel. LF refers to Lead Free package. This device is WEEE and RoHS compliant 1 ...

Page 2

... Pad configuration versus chip modes .......................................................................................................................... 40 8 Application information ............................................................................................................................................ 41 8.1 Matching network of the receiver ................................................................................................................................. 41 8.2 Matching network of the transmitter............................................................................................................................. 41 8.3 VCO tank ..................................................................................................................................................................... 44 8.4 Loop filter of the frequency synthesizer ....................................................................................................................... 45 8.5 Reference crystal for the frequency synthesizer .......................................................................................................... 46 9 Packaging information .............................................................................................................................................. 47 © Semtech 2008 TABLE OF CONTENTS 2 XE1205 www.semtech.com ...

Page 3

... N5K3760B and N5K6993) exhibit a non-conformance to specification. The non-conformance affects the FIFO buffer described in section 5.2.5. Please use the FIFO in this product only in conjunction with the Technical Note TN1205.01 (available www.semtech.com). All other date-codes are in conformance with the specification. 2 FUNCTIONAL BLOCK DIAGRAM ...

Page 4

... TMOD(2) I/O 45 TMOD(1) I/O 46 TMOD(0) I © Semtech 2008 DESCRIPTION Pad below package (should be grounded) Transmit/Receive/Stand-by/Sleep Mode Select Transmit/Receive/Stand-by/Sleep Mode Select Not connected (should be grounded) Not connected (should be grounded) RF Input RF Input Power Amplifier Ground Power Amplifier Ground RF Output Power Amplifier Supply Voltage ...

Page 5

... Frequency deviation CCR Co-channel rejection IIP3 Input intercept point (from LNA input to base-band filter output) BW Base band filter bandwidth (SSB) © Semtech 2008 Table 2: Absolute Maximum Operation Ranges Table 3: Operating Range Conditions Quartz oscillator (39 MHz) enabled RFOP = 5 dBm RFOP = 15 dBm Mode A ...

Page 6

... The 304.7kpbs max bit rate is guaranteed by validation. The max bit rate guaranteed by production test is 152.3 kbit/s (5) RSSI also available in mode B with higher thresholds as described in section 5.2.3.4 © Semtech 2008 Conditions funw = kHz single tone ...

Page 7

... Operation of the XE1205 over the frequency range 180 MHz - 1000 MHz beyond the ISM bands described above can be achieved by modifying the reference oscillator crystal frequency. Please contact Semtech for more details. The XE1205 is programmed by a microcontroller through the 3-wire fully-compatible SPI serial bus (MOSI, MISO, and SCK) to write to and read from the configuration registers ...

Page 8

... DCLK. The function of the bit synchronizer is to remove glitches from the data stream and to provide a synchronous clock at DCLK. The output DATA is valid at the rising edge of DCLK. The following diagram shows the receiver chain operating in this mode © Semtech 2008 IRQ_0 0 Output ...

Page 9

... For best operation of the demodulator it is recommended the modulation index β of the input signal meets the following condition: Δ β ≥ where Δf is the frequency deviation and BR the bit rate. © Semtech 2008 RXParam_Disable_bitsync data BIT SYNCHRONIZER dclk RX aram_Pattern RSSI_irq Figure 2: Receiver chain in continuous mode 9 XE1205 ...

Page 10

... If needed possible to select intermediate bit rates by changing the Over-Sampling Ratio (OSR) of the bit synchronizer, whose default value is 32. The latter can be superseded by setting high the register TParam_Chg_OSR. In this case, the bit rate becomes: 152 . ⋅ Bit rate = + int(Br(6 : 0)) 1 int( OSR © Semtech 2008 Figure 3: Bit synchronizer timing diagram XE1205 www.semtech.com ...

Page 11

... VTHRi values may be selected. An additional way to increase RSSI operating range is to combine modes A and B thresholds. One could then cover input signals ranging from -110dBm (VTHR1, low range, mode -70dBm (VTHR3, high range, mode B) © Semtech 2008 Bit N-1 = Bit N = ...

Page 12

... IRQParam_RSSI_signal_detect. If the bit IRQParam_RSSI_int remains high, the process starts again. The next figure shows the timing diagram of RSSI in interrupt mode. IRQParam_RSSI_int RSSI_out_int IRQParam_RSSI_signal_detect IRQParam_RSSI_thr = “10” RSSI_irq Figure 6: RSSI generating interrupt signal when detecting a threshold © Semtech 2008 Read RSSI TS_RSSIM val1 val2 xxx val1 Figure 5: RSSI measurement timing diagram ...

Page 13

... DF), and FilterBW is the channel filter bandwidth defined by RXParam_BW(1:0) parameters. The frequency error can be calculated by the following formula: The frequency error = 500*int(FEI_out(15:0 Where int(x) is the integer value of the signed binary representation of x. © Semtech 2008 Read RSSI TS_FEI TS_FEI XXX ...

Page 14

... IRQParam_Start_detect bit is also asserted. This internal signal may be mapped to the IRQ_0 output using interrupt signal mapping (please refer to section 5.2.2). Once a pattern match has occurred, the pattern recognition block will remain inactive until IRQParam_Start_detect is re-asserted. © Semtech 2008 _FEI_out (15:0) represents the RXParam ...

Page 15

... FIFO, resets all FIFO status flags and re-initiates pattern matching (only when an overrun has occurred). In order to clear the FIFO in reception, a “1” should be written in IRQParam_start_detect (bit 6 add 6). Pattern matching can also be re-initiated during a FIFO filling sequence by writing a ‘1’ to IRQParam_Start_detect. © Semtech 2008 RXParam_Pattern = ‘1’ ...

Page 16

... IRQParam_RX_irq_0 is set to “10” (please refer to section 5.2.2). Alternatively, the WRITE_BYTE signal may also be used as an interrupt if IRQParam_RX_irq_0 is set to “01”. 5.2.5.1 Demodulator in buffered mode Demodulation in buffered mode occurs in the same way as in continuous mode (section 5.2.3.1). Received data is directly read from the FIFO and the DATA pin is not used. © Semtech 2008 ...

Page 17

... It can be seen from table 9 that this option also allows the sensitivity to be improved for very low deviations. © Semtech 2008 d mode tion operates the same way as in continuous mode. In buffered -band filter which can be selected by changing only a 2-bit word in the configuration lectivity of the receiver for very narrow-band applications ...

Page 18

... DCLK and filtered. Figure 12 shows an example of filtered data for a bit rate of 4.8kbit/s and a frequency deviation of 5 kHz: © Semtech 2008 an (optional) pulse shaping filter can be used resulting in an adjacent channel via the SPI interface; data from the FIFO is used to ...

Page 19

... The filtering option can be used for all bit rates specified in section 5.2.3.2 and for the following frequency deviations. Table 11: © Semtech 2008 Figure 12: Pre-filtering of bit stream in transmit mode Freq_dev(8:0) Frequency deviation (kHz) 000000101 000001010 000010100 000101000 001010000 010100000 101000000 Available frequ ...

Page 20

... IRQ_1 is mapped to IRQParam_Fifofull signal indicating that the transmission FIFO is full when IRQParam_Tx_irq_1 is set to ‘0’ and to TX_stopped when IRQParam_Tx_irq_1 is set to ‘1’. IRQ_0 is mapped to the /fifoempty signal; this signal is used to indicate that the transmission FIFO is empty and must be refilled with data to continue data transmission. © Semtech 2008 0 Data shift register ...

Page 21

... CLKOUT is defined by the value of the OSCParam_Clkout_freq(2:0) parameter. The output frequency at CLKOUT is the reference oscillator frequency divided 32. With a reference oscillator frequency of 39 MHz this provides a reference clock at 19.5 MHz, 9.75 MHz, 4.87 MHz, 2.44 MHz or 1.22 MHz, respectively. This clock signal is disabled in Sleep Mode. © Semtech 2008 21 XE1205 www.semtech.com ...

Page 22

... Tx filter Tx filter is also available at 304.7 kbit/s operation and although not compulsory, its use is recommended to reduce spectrum bandwidth. Contrary to the other bitrates, an additional specific bit must be set. Consequently, following settings should be programmed: Name Filter 304 kbit/s_filter © Semtech 2008 Address Bits Value ( ...

Page 23

... Please note that all features including FIFO are available at bit rates up to 304.7 kbit/s. 6.4 TYPICAL PERFORMANCE • Sensitivity@0.1%: -102 dBm in mode A and -90 dBm in mode B. • ACR@1MHz offset, single tone: 25 dBc. © Semtech 2008 434 MHz 869 MHz 915 MHz 3 220 pF ...

Page 24

... NSS_DATA is high, the counters controlling transmission are reset. Reception starts with the first clock cycle after the falling edge of NSS_CONFIG or NSS_DATA; if either signal goes high during a byte transmission the counters are reset and the byte has to be retransmitted. © Semtech 2008 NSS_CONFIG MOSI ...

Page 25

... NSS_CONFIG does not need to make a high to low transmission between two write sequences. The bytes are alternatively considered as an address byte followed by a data byte. The read sequence via the SPI_CONFIG interface is similar to the write one except that the data byte contains all zeroes © Semtech 2008 shows the timing diagram for a typical write sequence: 4 ...

Page 26

... The operations with SPI_DATA interface are similar to those with SPI_CONFIG except that there is only a data byte (no address byte is required) and except that it is necessary to toggle the NSS_DATA signal back to high and back to low between each transmitted or received byte. © Semtech 2008 4 5 ...

Page 27

... SCK MOSI MISO HZ D1(7) D1(6) D1(5) NSS_DATA Note that it is necessary to toggle NSS_DATA signal back to high and then back to low between each transmitted and received byte. © Semtech 2008 D1(4) D1(3) D1(2) D1(1) D1(0) D2(7) D2(6) D2(5) D2(4) x Byte 1 to read ...

Page 28

... TXParam RXParam OSCParam TParam All the bits that are referred to as “reserved” in this section should be set to “0” during write operations. © Semtech 2008 Address Description 0-4 Main parameters common to transmit and receive modes 5-6 Interrupt registers 7 Transmitter parameters ...

Page 29

... Freq_dev( Freq_dev(7:0) 7 Knx Br(6:0) 6-0 2 © Semtech 2008 Description r/w Transceiver mode: 00 -> sleep mode 01 -> receive mode 10 -> transmit mode 11 -> stand-by mode r/w Transceiver mode selection: 0 -> mode defined by MCParam_chip_mode, SW(1: output sleep mode -> SW(1:0) = ”00” receiver mode -> ...

Page 30

... Start_fill 7 6 Start_detect 6 6 © Semtech 2008 Description r/w LO frequency in 2’s complement: r/w 00…0 -> Flo = middle of the range 0X…X-> Flo = higher than the middle of the range 1X…X-> Flo = lower than the middle of the range Example: 00…001 -> Flo = middle of the range + FSTEP ...

Page 31

... Name Disable_bitsync 7 8 BW(1:0) 6-5 8 Max_BW 4 8 © Semtech 2008 RW Description r Transmission stopped ( IRQ source) r/w 0 -> Start transmission when the FIFO is full 1 -> Start transmission when FIFO is not empty (/fifoempty = ‘1’) r/w Enable interrupt RSSI_irq when RSSI_thr is reached: 0 -> no interrupt generated 1 -> ...

Page 32

... Rmode 5 10 Pattern 4 10 Psize(1:0) 3-2 10 © Semtech 2008 RW Description (about 400 kHz SSB) and disables calibration: 0 -> bandwidth defined by BW(1:0) 1 -> bandwidth forced to its maximal value r/w Calibration of the bandwidth of the base band filter: 00 -> calibration at start up 01 -> no calibration 10 -> ...

Page 33

... Byte Address 13 14 Bit 7 Bit 0 Bit 7 10010011 Xxxxxxxx 101 10010011 previous bits from last bit received demodulator © Semtech 2008 RW Description r/w Number of tolerated errors for the pattern recognition: 00 -> 0 error 01 -> 1 error 10 -> 2 errors 11 -> 3 errors r FEI output 2’s complement representation ...

Page 34

... Resxosc 7-4 18 304 kbit/s_filter 3 18 RESERVED 2-0 18 © Semtech 2008 RW Description r/w Sources of reference frequency 0 -> internal quartz oscillator (for XTAL or TCXO) 1 -> external signal applied on pin XTA (CMOS type signal, external clock) r/w Enable clkout 0 -> no signal provided on pin CLKOUT 1 -> ...

Page 35

... Add_HPF(2:0) 5-3 22 Chg_OSR 4 27 OSR 7-0 28 © Semtech 2008 RW Description Change of RXParam_BW(1:0) decoding, allowing additional r/w bandwidths for the base-band filter to be selected: Add_BW = 0 -> default values of RXParam_BW(1:0): RXParam_BW(1: => 10 kHz RXParam_BW(1: => 20 kHz RXParam_BW(1: => 40 kHz RXParam_BW(1: => 200 kHz Add_BW = 1 -> ...

Page 36

... Figure 19 Sequence from sleep mode to receive mode via standby mode. The sequence from sleep to transmit mode via stand-by mode is displayed in Figure 20. TS_STR is the initialization time of the frequency synthesizer and the power amplifier. © Semtech 2008 Table 26 below. These modes are defined by register ...

Page 37

... Figure 21 Sequence from transmit to receive mode. Figure 22 represents the sequence from receive to transmit mode. TS_TR is the initialization time of the power amplifier if the frequency synthesizer is already enabled: Programmed mode NSS_CONFIG Actual mode © Semtech 2008 Stand-by Stand-by TS_OS . TS_RE is the initialization time of the receiver base Transmit Transmit ...

Page 38

... MHz fundamental mode quartz crystal or with a 3 overtone operation requires an internal resistor to be connected in parallel with the crystal. This resistor can be connected by programming the register OSCParam_Resxosc(3:0). The required value depends on the crystal © Semtech 2008 receive f1 ...

Page 39

... NSS_CONFIG pin causes the registers to be updated and this will result in CLKOUT being disabled. For this reason the first programming sequence should be to enable CLKOUT by setting OSCParam_Clkout to high for applications using CLKOUT recommended to initialize the XE1205 registers immediately after power-up. © Semtech 2008 UT clock frequency is provided for a microcontroller or external circuitry. A CLKOUT frequency 000 1 ...

Page 40

... DATA OUTPUT CLKOUT OUTPUT if MISO NSS_CONFIG=’0’ or NSS_DATA = ‘0’ else High Impedance INPUT MOSI INPUT SCK © Semtech 2008 Standby Receive OUTPUT when OUTPUT when Select_mode = ‘0’ Select_mode = ‘0’ else else Input Input OUTPUT when OUTPUT when Select mode = ‘ ...

Page 41

... The optimum load impedances for 15 dBm output power at the three main frequencies are given in Table 30. PA optimum load 0 dBm 5 dBm 10 dBm 15 dBm Table 30: Optimum load impedances for 15dBm output power © Semtech 2008 CR1 LR1 CR2 VSS Figure 25 Matching network at the input of the receiver. Typical Value for 869 MHz 1 ...

Page 42

... Figure 27 below show contours of output power versus load impedance when the highest output level is selected (15 dBm mode). 0.4 0.3 0.2 0.1 0.1 0.2 0.1 0.2 0.3 0.4 Figure 26: Output power vs. load impedance at 869 MHz. © Semtech 2008 869 MHz 15 dBm 0.8 0.9 1 1.2 0.6 0.5 15 dBm 0 dBm 1 2 dBm 0.5 0.6 1 ...

Page 43

... Figure 27: Output power vs. load impedance at 915 MHz. © Semtech 2008 915 MHz 15 dBm 1 15 dBm 0 dBm 12 dBm 1 43 XE1205 www.semtech.com ...

Page 44

... LT3 8.3 VCO TANK The VCO tank circuit should implemented with an inductor and capacitor in parallel. Typical component values are shown in Table 32. Name CV1 LV1 © Semtech 2008 CT2 LT3 CT3 LT2 Typical Value Typical Value for 869 MHz for 915 MHz 6 ...

Page 45

... Typical recommended component values for the frequency synthesizer loop filter are provided in Table 33 below: Name CL1 CL2 RL1 Table 33: Typical frequency synthesizer component values For 304.7 kbit/s operation, refer to section 6. © Semtech 2008 RL1 CL2 CL1 VSS Figure 29: Frequency synthesizer loop filter 434 MHz ...

Page 46

... BWssb is the single side-band bandwidth of the signal, and BWfilter is the single side-band bandwidth of the base-band filter. The overtone crystal usage can result in higher oscillator start-up time than fundamental mode. The overtone crystal should be designed for Cload = and has parameters of Rm < 60Ω, C0 < 7 pF. © Semtech 2008 Min. value - - ...

Page 47

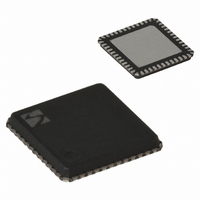

... PACKAGING INFORMATION XE1205 comes in a 48-lead VQFN 8X8 package as shown in Figure 30 © Semtech 2008 below. Figure 30: Package dimensions 47 XE1205 www.semtech.com ...

Page 48

... No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights. Semtech assumes no responsibility or liability whatsoever for any failure or unexpected operation resulting from misuse, neglect improper installation, repair or improper handling or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified range ...