MCIMX53-START Freescale Semiconductor, MCIMX53-START Datasheet - Page 13

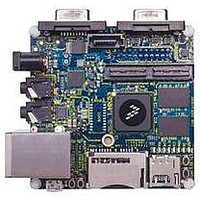

MCIMX53-START

Manufacturer Part Number

MCIMX53-START

Description

KIT DEVELOPMENT I.MX53

Manufacturer

Freescale Semiconductor

Series

i.MX53r

Type

MCUr

Datasheets

1.MCIMX53-START.pdf

(2 pages)

2.MCIMX53-START.pdf

(180 pages)

3.MCIMX53-START.pdf

(204 pages)

Specifications of MCIMX53-START

Contents

Board

Silicon Manufacturer

Freescale

Core Architecture

ARM

Core Sub-architecture

Cortex - A8

Silicon Core Number

I.MX5

Silicon Family Name

I.MX53

Peak Reflow Compatible (260 C)

Yes

Rohs Compliant

Yes

Leaded Process Compatible

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

For Use With/related Products

i.MX53

Lead Free Status / Rohs Status

Supplier Unconfirmed

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Freescale Semiconductor

Mnemonic

SAHARA

SCCv2

SDMA

Block

RTIC

SATA

Real Time

Integrity Checker

SAHARA

Security

Accelerator

Serial ATA

Security

Controller, ver. 2

Smart Direct

Memory Access

Block Name

i.MX53xD Applications Processors for Consumer Products, Rev. 1

Table 2. i.MX53xD Digital and Analog Blocks (continued)

Security

Security

Connectivity

Peripherals

Security

System

Control

Peripherals

Subsystem

Protecting read only data from modification is one of the basic elements in

trusted platforms. The run-time integrity checker, version 3 (RTIC) block is

a data-monitoring device responsible for ensuring that the memory content

is not corrupted during program execution. The RTIC mechanism

periodically checks the integrity of code or data sections during normal OS

run-time execution without interfering with normal operation. The purpose

of the RTIC is to ensure the integrity of the peripheral memory contents,

protect against unauthorized external memory elements replacement and

assist with boot authentication.

SAHARA (symmetric/asymmetric hashing and random accelerator),

version 4, is a security coprocessor. It implements symmetric encryption

algorithms, (AES, DES, 3DES, RC4 and C2), public key algorithms (RSA

and ECC), hashing algorithms (MD5, SHA-1, SHA-224 and SHA-256), and

a hardware true random number generator. It has a slave IP Bus interface

for the host to write configuration and command information, and to read

status information. It also has a DMA controller, with an AHB bus interface,

to reduce the burden on the host to move the required data to and from

memory.

SATA HDD interface, includes the SATA controller and the PHY. It is a

complete mixed-signal IP solution for SATA HDD connectivity.

The security controller is a security assurance hardware module designed

to safely hold sensitive data, such as encryption keys, digital right

management (DRM) keys, passwords and biometrics reference data. The

SCCv2 monitors the system’s alert signal to determine if the data paths to

and from it are secure, that is, it cannot be accessed from outside of the

defined security perimeter. If not, it erases all sensitive data on its internal

RAM. The SCCv2 also features a key encryption module (KEM) that allows

non-volatile (external memory) storage of any sensitive data that is

temporarily not in use. The KEM utilizes a device-specific hidden secret key

and a symmetric cryptographic algorithm to transform the sensitive data

into encrypted data.

The SDMA is multi-channel flexible DMA engine. It helps in maximizing

system performance by off loading various cores in dynamic data routing.

The SDMA features list is as follows:

• Powered by a 16-bit instruction-set micro-RISC engine

• Multi-channel DMA supports up to 32 time-division multiplexed DMA

• 48 events with total flexibility to trigger any combination of channels

• Memory accesses including linear, FIFO, and 2D addressing

• Shared peripherals between ARM and SDMA

• Very fast context-switching with two-level priority-based preemptive

• DMA units with auto-flush and prefetch capability

• Flexible address management for DMA transfers (increment, decrement,

• DMA ports can handle unidirectional and bidirectional flows (copy mode)

• Up to 8-word buffer for configurable burst transfers to / from the EXTMC

• Support of byte swapping and CRC calculations

• A library of scripts and API is available

channels

multi-tasking

and no address changes on source and destination address)

Brief Description

Modules List

13