CY8C3665AXI-016 Cypress Semiconductor Corp, CY8C3665AXI-016 Datasheet - Page 24

CY8C3665AXI-016

Manufacturer Part Number

CY8C3665AXI-016

Description

CY8C3665AXI-016

Manufacturer

Cypress Semiconductor Corp

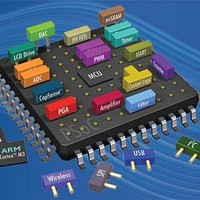

Series

PSOC™ 3 CY8C36xxr

Specifications of CY8C3665AXI-016

Core Processor

8051

Core Size

8-Bit

Speed

67MHz

Connectivity

EBI/EMI, I²C, LIN, SPI, UART/USART, USB

Peripherals

CapSense, DMA, POR, PWM, WDT

Number Of I /o

62

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Eeprom Size

1K x 8

Ram Size

4K x 8

Voltage - Supply (vcc/vdd)

1.71 V ~ 5.5 V

Data Converters

A/D 2x12b, D/A 4x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

*

Processor Series

CY8C36

Core

8051

Data Bus Width

32 bit

Data Ram Size

8 KB

Interface Type

I2C, SPI, UART, USB

Maximum Clock Frequency

67 MHz

Number Of Programmable I/os

28 to 72

Number Of Timers

4

Operating Supply Voltage

0.5 V to 5.5 V

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Controller Family/series

(8051) PSOC 3

No. Of I/o's

62

Eeprom Memory Size

1KB

Ram Memory Size

4KB

Cpu Speed

67MHz

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

CY8C3665AXI-016

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

Company:

Part Number:

CY8C3665AXI-016T

Manufacturer:

Cypress Semiconductor Corp

Quantity:

10 000

I/O Port SFRs

The I/O ports provide digital input sensing, output drive, pin

interrupts, connectivity for analog inputs and outputs, LCD, and

access to peripherals through the DSI. Full information on I/O

ports is found in

I/O ports are linked to the CPU through the PHUB and are also

available in the SFRs. Using the SFRs allows faster access to a

limited set of I/O port registers, while using the PHUB allows boot

configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

5.7.3.1 xdata Space

The 8051 xdata space is 24-bit, or 16 MB in size. The majority of

this space is not “external”—it is used by on-chip components.

See

accessed using the EMIF. See

page 22.

Document Number: 001-53413 Rev. *K

SFRPRTxDR sets the output data state of the port (where × is

port number and includes ports 0–6, 12 and 15).

The SFRPRTxSEL selects whether the PHUB PRTxDR

register or the SFRPRTxDR controls each pin’s output buffer

within the port. If a SFRPRTxSEL[y] bit is high, the

corresponding SFRPRTxDR[y] bit sets the output state for that

pin. If a SFRPRTxSEL[y] bit is low, the corresponding

PRTxDR[y] bit sets the output state of the pin (where y varies

from 0 to 7).

The SFRPRTxPS is a read only register that contains pin state

values of the port pins.

Table

5-5. External, that is, off-chip, memory can be

I/O System and Routing

External Memory Interface

on page 32.

on

Table 5-5. XDATA Data Address Map

0×00 0000 – 0×00 1FFF

0×00 4000 – 0×00 42FF

0×00 4300 – 0×00 43FF

0×00 4400 – 0×00 44FF

0×00 4500 – 0×00 45FF

0×00 4700 – 0×00 47FF

0×00 4900 – 0×00 49FF

0×00 4E00 – 0×00 4EFF

0×00 4F00 – 0×00 4FFF

0×00 5000 – 0×00 51FF

0×00 5400 – 0×00 54FF

0×00 5800 – 0×00 5FFF

0×00 6000 – 0×00 60FF

0×00 6400 – 0×00 6FFF

0×00 7000 – 0×00 7FFF

0×00 8000 – 0×00 8FFF

0×00 A000 – 0×00 A400

0×00 C000 – 0×00 C800

0×01 0000 – 0×01 FFFF

0×05 0220 – 0×05 02F0

0×08 0000 – 0×08 1FFF

0×80 0000 – 0×FF FFFF

Address Range

PSoC

®

SRAM

Clocking, PLLs, and oscillators

Power management

Interrupt controller

I

Decimator

(EMIF) control registers

Analog Subsystem interface

CAN

Digital Filter Block

configuration

Debug controller

flash ECC bytes

Ports interrupt control

Flash programming interface

Fixed timer/counter/PWMs

I/O ports control

External Memory Interface

USB controller

UDB configuration

PHUB configuration

EEPROM

Digital Interconnect

External Memory Interface

2

C controller

3: CY8C36 Family

Purpose

Data Sheet

Page 24 of 125

[+] Feedback