ISPGDX80VA-3TN100 Lattice, ISPGDX80VA-3TN100 Datasheet - Page 11

ISPGDX80VA-3TN100

Manufacturer Part Number

ISPGDX80VA-3TN100

Description

Analog & Digital Crosspoint ICs PROGRAMMABLE GEN DIG CROSSPOINT

Manufacturer

Lattice

Datasheet

1.ISPGDX80VA-3TN100.pdf

(24 pages)

Specifications of ISPGDX80VA-3TN100

Maximum Dual Supply Voltage

1.95 V

Mounting Style

SMD/SMT

Number Of Arrays

1

Operating Supply Voltage

3.3 V

Supply Type

Single

Configuration

40 x 40

Package / Case

PLCC-28

Input Level

TTL

Output Level

LVTTL, TTL

Supply Voltage (max)

3.6 V

Supply Voltage (min)

3 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Product

Digital Crosspoint

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISPGDX80VA-3TN100

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

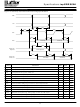

1. All timings measured with one output switching, fast output slew rate setting, except

2. The delay parameters are measured with Vcc as I/O voltage reference. An additional 0.5ns delay is incurred when Vccio is

3. The new “-3” speed grade (tpd = 3.0ns) will be effective starting with date code A113xxxx. Devices with topside date codes

t

t

f

f

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

PARAMETER

External Timing Parameters

pd

sel

max (Tog.)

max (Ext.)

su1

su2

su3

su4

suce1

suce2

suce3

h1

h2

h3

h4

hce1

hce2

hce3

gco1

gco2

co1

co2

en

dis

toeen

toedis

wh

wl

rst

rw

sl

sk

used as I/O voltage reference.

prior to A113xxxx adhere to the shaded “-3” speed grade (tpd = 3.5ns).

2

2

2

2

2

2

2

2

2

2

COND.

TEST

A

A

A

A

A

A

B

C

B

C

D

A

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

1

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

#

1

2

3

4

5

6

7

8

9

Data Prop. Delay: Any I/O Pin to Any I/O Pin (4:1 MUX)

Data Prop. Delay: MUXsel Inputs to Any Output (4:1 MUX)

Clk. Frequency, Max. Toggle

Clk. Frequency with External Feedback

Input Latch or Reg. Setup Time Before Y

Input Latch or Reg. Setup Time Before I/O Clk.

Output Latch or Reg. Setup Time Before Y

Output Latch or Reg. Setup Time Before I/O Clk.

Global Clk. Enable Setup Time Before Y

Global Clk. Enable Setup Time Before I/O Clk.

I/O Clk. Enable Setup Time Before Y

Input Latch or Reg. Hold Time (Y

Input Latch or Reg. Hold Time (I/O Clk.)

Output Latch or Reg. Hold Time (Y

Output Latch or Reg. Hold Time (I/O Clk.)

Global Clk. Enable Hold Time (Y

Global Clk. Enable Hold Time (I/O Clk.)

I/O Clk. Enable Hold Time (Y

Output Latch or Reg. Clk. (from Y

Input Latch or Register Clk. (from Y

Output Latch or Reg. Clk. (from I/O pin) to Output Delay

Input Latch or Reg. Clk. (from I/O pin) to Output Delay

Input to Output Enable

Input to Output Disable

Test OE Output Enable

Test OE Output Disable

Clock Pulse Duration, High

Clock Pulse Duration, Low

Register Reset Delay from RESET Low

Reset Pulse Width

Output Delay Adder for Output Timings Using Slow Slew Rate

Output Skew (tgco1 Across Chip)

Over Recommended Operating Conditions

DESCRIPTION

x

)

x

x

x

)

) to Output Delay

)

x

)

x

) to Output Delay

x

11

(

x

x

tsu3+tgco1

x

1

Specifications ispGDX80VA

)

208.3

MIN. MAX.

250

2.2

1.8

1.8

1.5

1.8

1.5

2.5

0.0

0.5

0.0

0.5

0.0

1.0

0.0

2.0

2.0

4.5

–

–

–

–

–

–

–

–

–

–

–

–

–

-3

t

3

sl

3.0

3.2

3.0

5.5

3.5

6.0

4.0

4.0

5.5

5.5

7.0

3.0

0.5

.

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

166.7

MIN. MAX.

250

3.0

2.5

2.5

2.0

2.5

1.5

3.0

0.0

0.5

0.0

1.0

0.0

1.0

0.0

2.0

2.0

5.0

–

–

–

–

–

–

–

–

–

–

–

–

–

-3

3.5

3.5

3.5

6.0

4.0

7.0

5.0

5.0

6.0

6.0

8.0

3.5

0.5

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

MIN. MAX.

10.0

143

111

4.0

3.0

4.0

3.0

2.5

1.5

4.5

0.0

1.5

0.0

1.5

0.0

1.5

0.0

3.5

3.5

–

–

–

–

–

–

–

–

–

–

–

–

–

-5

14.0

5.0

5.0

5.0

8.5

6.0

9.5

6.0

6.0

6.0

6.0

5.0

0.5

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

–

UNITS

MHz

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns