ISPGDX80VA-3TN100 Lattice, ISPGDX80VA-3TN100 Datasheet - Page 14

ISPGDX80VA-3TN100

Manufacturer Part Number

ISPGDX80VA-3TN100

Description

Analog & Digital Crosspoint ICs PROGRAMMABLE GEN DIG CROSSPOINT

Manufacturer

Lattice

Datasheet

1.ISPGDX80VA-3TN100.pdf

(24 pages)

Specifications of ISPGDX80VA-3TN100

Maximum Dual Supply Voltage

1.95 V

Mounting Style

SMD/SMT

Number Of Arrays

1

Operating Supply Voltage

3.3 V

Supply Type

Single

Configuration

40 x 40

Package / Case

PLCC-28

Input Level

TTL

Output Level

LVTTL, TTL

Supply Voltage (max)

3.6 V

Supply Voltage (min)

3 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Product

Digital Crosspoint

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISPGDX80VA-3TN100

Manufacturer:

Lattice Semiconductor Corporation

Quantity:

10 000

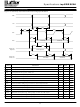

1. Internal Timing Parameters are not tested and are for reference only.

2. The new “-3” speed grade (tpd = 3.0ns) will be effective starting with date code A113xxxx. Devices with topside date codes prior to

PARAMETER

Internal Timing Parameters

Inputs

t

GRP

t

MUX

t

t

t

t

t

t

Register

t

t

t

t

t

t

t

Data Path

t

t

t

t

t

t

t

Outputs

t

t

t

t

t

t

Clocks

t

t

t

t

t

t

Global Reset

io

grp

muxd

muxexp

muxs

muxsio

muxsg

muxselexp

iolat

iosu

ioh

ioco

ior

cesu

ceh

fdbk

iobp

ioob

muxcg

muxcio

iodg

iodio

ob

obs

oeen

oedis

goe

toe

ioclk

gclk

gclkeng

gclkenio

ioclkeng

gr

A113xxxx adhere to the shaded “-3” speed grade (tpd = 3.5ns).

32 Input Buffer Delay

33 GRP Delay

34 I/O Cell MUX A/B/C/D Data Delay

35 I/O Cell MUX A/B/C/D Expander Delay

36 I/O Cell Data Select

37 I/O Cell Data Select (I/O Clock)

38 I/O Cell Data Select (Yx Clock)

39 I/O Cell MUX Data Select Expander Delay

40 I/O Latch Delay

41 I/O Register Setup Time Before Clock

42 I/O Register Hold Time After Clock

43 I/O Register Clock to Output Delay

44 I/O Reset to Output Delay

45 I/O Clock Enable Setup Time Before Clock

46 I/O Clock Enable Hold Time After Clock

47 I/O Register Feedback Delay

48 I/O Register Bypass Delay

49 I/O Register Output Buffer Delay

50 I/O Register A/B/C/D Data Input MUX Delay (Yx Clock)

51 I/O Register A/B/C/D Data Input MUX Delay (I/O Clock)

52 I/O Register I/O MUX Delay (Yx Clock)

53 I/O Register I/O MUX Delay (I/O Clock)

54 Output Buffer Delay

55 Output Buffer Delay (Slow Slew Option)

56 I/O Cell OE to Output Enable

57 I/O Cell OE to Output Disable

58 GRP Output Enable and Disable Delay

59 Test OE Enable and Disable Delay

60 I/O Clock Delay

61 Global Clock Delay

62 Global Clock Enable (Yx Clock)

63 Global Clock Enable (I/O Clock)

64 I/O Clock Enable (Yx Clock)

65 Global Reset to I/O Register Latch

#

Over Recommended Operating Conditions

DESCRIPTION

1

14

Specifications ispGDX80VA

MIN. MAX. MIN. MAX. MIN. MAX. UNITS

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

-3

2

0.3

1.1

0.8

1.3

1.0

1.5

1.5

1.5

1.0

0.4

1.4

0.9

1.0

0.6

1.2

0.4

0.0

0.0

1.3

1.3

3.1

3.1

0.8

3.8

2.6

2.6

0.0

2.5

0.3

1.3

2.5

2.0

1.5

5.2

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

-3

0.4

1.1

1.0

1.5

1.0

1.5

1.5

1.5

1.0

0.8

1.7

1.2

1.0

1.3

1.2

0.4

0.0

0.0

1.5

1.5

3.5

3.5

1.0

4.5

3.5

3.5

0.0

2.5

0.3

1.3

2.5

2.0

1.5

6.0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

-5

11.0

0.9

1.1

1.5

2.0

1.5

3.0

2.0

2.0

1.0

2.0

1.5

0.5

1.5

2.0

0.5

0.9

0.0

0.0

2.0

3.0

4.0

5.0

1.5

6.5

4.0

4.0

0.0

2.0

2.0

2.0

2.5

3.5

2.5

Timing Rev. 2.9

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns