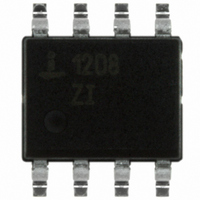

ISL1208IB8Z-TK Intersil, ISL1208IB8Z-TK Datasheet - Page 12

ISL1208IB8Z-TK

Manufacturer Part Number

ISL1208IB8Z-TK

Description

IC RTC LP BATT BACKED SRAM 8SOIC

Manufacturer

Intersil

Type

Clock/Calendar/NVSRAMr

Datasheet

1.ISL1208IB8Z-TK.pdf

(24 pages)

Specifications of ISL1208IB8Z-TK

Memory Size

2B

Time Format

HH:MM:SS (12/24 hr)

Date Format

YY-MM-DD-dd

Interface

I²C, 2-Wire Serial

Voltage - Supply

2.7 V ~ 5.5 V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

8-SOIC (3.9mm Width)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

ISL1208IB8Z-TKTR

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ISL1208IB8Z-TK

Manufacturer:

STC

Quantity:

1 000

Part Number:

ISL1208IB8Z-TK

Manufacturer:

INTERSIL

Quantity:

20 000

Real Time Clock Registers

Addresses [00h to 06h]

RTC REGISTERS (SC, MN, HR, DT, MO, YR, DW)

These registers depict BCD representations of the time. As

such, SC (Seconds) and MN (Minutes) range from 0 to 59,

HR (Hour) can either be a 12-hour or 24-hour mode, DT

(Date) is 1 to 31, MO (Month) is 1 to 12, YR (Year) is 0 to 99,

and DW (Day of the Week) is 0 to 6.

The DW register provides a Day of the Week status and uses

three bits DW2 to DW0 to represent the seven days of the

week. The counter advances in the cycle 0-1-2-3-4-5-6-0-1-

2-… The assignment of a numerical value to a specific day

of the week is arbitrary and may be decided by the system

software designer. The default value is defined as “0”.

24 HOUR TIME

If the MIL bit of the HR register is “1”, the RTC uses a 24-

hour format. If the MIL bit is “0”, the RTC uses a 12-hour

format and HR21 bit functions as an AM/PM indicator with a

“1” representing PM. The clock defaults to 12-hour format

time with HR21 = “0”.

LEAP YEARS

Leap years add the day February 29 and are defined as those

years that are divisible by 4. Years divisible by 100 are not leap

years, unless they are also divisible by 400. This means that

the year 2000 is a leap year, the year 2100 is not. The ISL1208

does not correct for the leap year in the year 2100.

Control and Status Registers

Addresses [07h to 0Bh]

The Control and Status Registers consist of the Status

Register, Interrupt and Alarm Register, Analog Trimming and

Digital Trimming Registers.

Status Register (SR)

The Status Register is located in the memory map at

address 07h. This is a volatile register that provides either

control or status of RTC failure, battery mode, alarm trigger,

write protection of clock counter, crystal oscillator enable and

auto reset of status bits.

Default

ADDR

07h

ARST XTOSCB reserved WRTC reserved ALM BAT RTCF

7

0

TABLE 2. STATUS REGISTER (SR)

6

0

5

0

12

4

0

3

0

2

0

1

0

0

0

ISL1208

REAL TIME CLOCK FAIL BIT (RTCF)

This bit is set to a “1” after a total power failure. This is a read

only bit that is set by hardware (ISL1208 internally) when the

device powers up after having lost all power to the device

(both V

whether V

the supplies does not set the RTCF bit to “1”. On power-up

after a total power failure, all registers are set to their default

states and the clock will not increment until at least one byte

is written to the clock register. The first valid write to the RTC

section after a complete power failure resets the RTCF bit to

“0” (writing one byte is sufficient).

BATTERY BIT (BAT)

This bit is set to a “1” when the device enters battery backup

mode. This bit can be reset either manually by the user or

automatically reset by enabling the auto-reset bit (see ARST

bit). A write to this bit in the SR can only set it to “0”, not “1”.

ALARM BIT (ALM)

These bits announce if the alarm matches the real time

clock. If there is a match, the respective bit is set to “1”. This

bit can be manually reset to “0” by the user or automatically

reset by enabling the auto-reset bit (see ARST bit). A write to

this bit in the SR can only set it to “0”, not “1”.

NOTE: An alarm bit that is set by an alarm occurring during an SR

read operation will remain set after the read operation is complete.

WRITE RTC ENABLE BIT (WRTC)

The WRTC bit enables or disables write capability into the

RTC Timing Registers. The factory default setting of this bit

is “0”. Upon initialization or power-up, the WRTC must be set

to “1” to enable the RTC. Upon the completion of a valid

write (STOP), the RTC starts counting. The RTC internal

1Hz signal is synchronized to the STOP condition during a

valid write cycle.

CRYSTAL OSCILLATOR ENABLE BIT (XTOSCB)

This bit enables/disables the internal crystal oscillator. When

the XTOSCB is set to “1”, the oscillator is disabled, and the

X1 pin allows for an external 32kHz signal to drive the RTC.

The XTOSCB bit is set to “0” on power-up.

AUTO RESET ENABLE BIT (ARST)

This bit enables/disables the automatic reset of the BAT and

ALM status bits only. When ARST bit is set to “1”, these

status bits are reset to “0” after a valid read of the respective

status register (with a valid STOP condition). When the

ARST is cleared to “0”, the user must manually reset the

BAT and ALM bits.

Interrupt Control Register (INT)

08h

Default

ADDR

TABLE 3. INTERRUPT CONTROL REGISTER (INT)

DD

IM ALME LPMODE FOBATB FO3 FO2 FO1 FO0

7

0

DD

and V

or V

6

0

BAT

BAT

go to 0V). The bit is set regardless of

is applied first. The loss of only one of

5

0

4

0

3

0

September 12, 2008

2

0

1

0

FN8085.8

0

0