ADSP-2184NKCA-320 Analog Devices Inc, ADSP-2184NKCA-320 Datasheet - Page 25

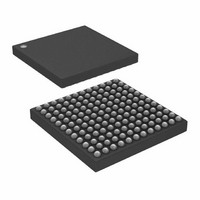

ADSP-2184NKCA-320

Manufacturer Part Number

ADSP-2184NKCA-320

Description

IC DSP 16BIT 80MHZ 144CSPBGA

Manufacturer

Analog Devices Inc

Series

ADSP-21xxr

Type

Fixed Pointr

Datasheet

1.ADSP-2185NKSTZ-320.pdf

(48 pages)

Specifications of ADSP-2184NKCA-320

Rohs Status

RoHS non-compliant

Interface

Host Interface, Serial Port

Clock Rate

80MHz

Non-volatile Memory

External

On-chip Ram

20kB

Voltage - I/o

3.30V

Voltage - Core

1.80V

Operating Temperature

0°C ~ 70°C

Mounting Type

Surface Mount

Package / Case

144-CSPBGA

Device Core Size

16b

Architecture

Enhanced Harvard

Format

Fixed Point

Clock Freq (max)

80MHz

Mips

80

Device Input Clock Speed

80MHz

Ram Size

20KB

Program Memory Size

Not RequiredKB

Operating Supply Voltage (typ)

1.8/2.5/3.3V

Operating Supply Voltage (min)

1.71V

Operating Supply Voltage (max)

1.89/3.6V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

144

Package Type

CSPBGA

Package

144CSP-BGA

Numeric And Arithmetic Format

Fixed-Point

Maximum Speed

80 MHz

Device Million Instructions Per Second

80 MIPS

Lead Free Status / Rohs Status

Not Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADSP-2184NKCA-320

Manufacturer:

Analog Devices Inc

Quantity:

10 000

ENVIRONMENTAL CONDITIONS

Table 14. Thermal Resistance

1

TEST CONDITIONS

Figure 19. Equivalent Loading for AC Measurements (Including All Fixtures)

Rating Description

Thermal Resistance (Case-

to-Ambient)

Thermal Resistance

(Junction-to-Ambient)

Thermal Resistance

(Junction-to-Case)

Where the Ambient Temperature Rating (T

Figure 18. Voltage Reference Levels for AC Measurements (Except Output

T

T

PD = Power Dissipation in W

AMB

CASE

= T

= Case Temperature in °C

CASE

OUTPUT

OUTPUT

INPUT

– (PD × θ

PIN

TO

CA

50pF

1

)

Enable/Disable)

Symbol

θ

θ

θ

CA

JA

JC

I

I

OL

OH

AMB

) is:

LQFP

(°C/W)

48

50

2

0.8V

1.5V

1.5V

2.0V

1.5V

Rev. A | Page 25 of 48 | August 2006

BGA

(°C/W)

63.3

70.7

7.4

Output Disable Time

Output pins are considered to be disabled when they have

stopped driving and started a transition from the measured out-

put high or low voltage to a high impedance state. The output

disable time (t

shown in

ence signal reaches a high or low voltage level to when the

output voltages have changed by 0.5 V from the measured out-

put high or low voltage.

The decay time, t

and the current load, i

mated by the following equation:

from which

is calculated. If multiple pins (such as the data bus) are disabled,

the measurement value is that of the last pin to stop driving.

Output Enable Time

Output pins are considered to be enabled when they have made

a transition from a high-impedance state to when they start

driving. The output enable time (t

a reference signal reaches a high or low voltage level to when the

output has reached a specified high or low trip point, as shown

in

the measurement value is that of the first pin to start driving.

REFERENCE

Figure

OUTPUT

(MEASURED)

(MEASURED)

SIGNAL

20. If multiple pins (such as the data bus) are enabled,

Figure

V

V

OH

OL

DIS

OUTPUT STOPS

) is the difference of t

20. The time is the interval from when a refer-

t

t

DECAY

t

Figure 20. Output Enable/Disable

DIS

DIS

MEASURED

DRIVING

t

HIGH-IMPEDANCE STATE. TEST CONDITIONS CAUSE

THIS VOLTAGE LEVEL TO BE APPROXIMATELY 1.5V.

DECAY

, is dependent on the capacitive load, C

L

=

, on the output pin. It can be approxi-

V

V

t

OH

MEASURED

OL

t

DECAY

(MEASURED) – 0.5V

(MEASURED) + 0.5V

=

C

----------------------- -

L

ENA

×

i

L

–

0.5V

) is the interval from when

MEASURED

t

DECAY

ADSP-218xN

OUTPUT STARTS

1.0V

2.0V

and t

DRIVING

t

ENA

DECAY

V

(MEASURED)

V

(MEASURED)

OH

OL

, as

L

,