DS2482X-101+T Maxim Integrated Products, DS2482X-101+T Datasheet - Page 14

DS2482X-101+T

Manufacturer Part Number

DS2482X-101+T

Description

IC MASTER I2C-1WIRE 1CH 9-WLP

Manufacturer

Maxim Integrated Products

Datasheet

1.DS2482X-101T.pdf

(24 pages)

Specifications of DS2482X-101+T

Controller Type

I²C Bus Controller

Interface

I²C

Voltage - Supply

2.9 V ~ 5.5 V

Current - Supply

750µA

Operating Temperature

-40°C ~ 85°C

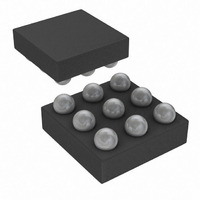

Mounting Type

Surface Mount

Package / Case

9-WLP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Single-Channel 1-Wire Master with Sleep Mode

Table 3. Bit Allocation in the Direction Byte

x = Don’t care.

14

Command Code

Command Parameter

Description

Typical Use

Restriction

Error Response

Command Duration

1-Wire Activity

Read Pointer Position

Status Bits Affected

Configuration Bits Affected

BIT 7

______________________________________________________________________________________

V

BIT 6

x

78h

Direction Byte

Generates three time slots: two read time slots and one write time slot at the 1-Wire line. The type

of write time slot depends on the result of the read time slots and the direction byte. The direction

byte determines the type of write time slot if both read time slots are 0 (a typical case). In this

case, the DS2482-101 generates a write-one time slot if V = 1 and a write-zero time slot if V = 0.

See Table 3.

If the read time slots are 0 and 1, they are followed by a write-zero time slot.

If the read time slots are 1 and 0, they are followed by a write-one time slot.

If the read time slots are both 1 (error case), the subsequent write time slot is a write-one.

To perform a 1-Wire Search ROM sequence; a full sequence requires this command to be

executed 64 times to identify and address one device.

1-Wire activity must have ended before the DS2482-101 can process this command.

Command code and direction byte is not acknowledged if 1WB = 1 at the time the command

code is received and the command is ignored.

3 x t

direction byte.

Begins maximum 262.5ns after the falling SCL edge of the MSB of the direction byte.

Status Register (for busy polling).

1WB (set to 1 for 3 x t

second t

1WS, APU apply.

SLOT

BIT 5

MSR

x

+ maximum 262.5ns, counted from the falling SCL edge of the first bit (MSB) of the

(i.e., at t

SLOT

SLOT

BIT 4

x

), SBR is updated at the first t

+ t

MSR

).

BIT 3

x

MSR

BIT 2

x

, TSB and DIR are updated at the

BIT 1

x

1-Wire Triplet

BIT 0

x