ADM8830ACP Analog Devices Inc, ADM8830ACP Datasheet - Page 4

ADM8830ACP

Manufacturer Part Number

ADM8830ACP

Description

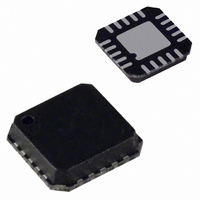

IC CHARGE PUMP REG TFT 20LFCSP

Manufacturer

Analog Devices Inc

Datasheet

1.ADM8830ARU-REEL.pdf

(8 pages)

Specifications of ADM8830ACP

Rohs Status

RoHS non-compliant

Applications

Converter, TFT, LCD

Voltage - Input

2.6 ~ 3.6 V

Number Of Outputs

3

Voltage - Output

-10.2V, 5.1V, 15.3V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

20-LFCSP

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADM8830ACP

Manufacturer:

TI

Quantity:

50 000

Company:

Part Number:

ADM8830ACP-REEL7

Manufacturer:

Alpha

Quantity:

99

Part Number:

ADM8830ACP-REEL7

Manufacturer:

ADI/亚德诺

Quantity:

20 000

Part Number:

ADM8830ACPZ

Manufacturer:

ADI/亚德诺

Quantity:

20 000

TSSOP

1, 2

3

4

5

6

7

8

9

10

11

12

13, 14

15, 16

17, 18

19

20

ADM8830

Pin Number

LFCSP

19, 20

1

2

3

4

5

6

7

8

9

10

11, 12

13, 14

15, 16

17

18

SCAN/BLANK

LDO_ON/OFF

+5VOUT

LDO_IN

VOUT

+5VIN

SHDN

C1+

C1–

V

CC

Mnemonic

C1–, C1+

V

VOUT

LDO_IN

+5VOUT

+5VIN

LDO_ON/OFF

SHDN

SCAN/BLANK

CLKIN

+15VOUT

C3–, C3+

C2–, C2+

C4–, C4+

–10VOUT

GND

CC

10

4

5

6

8

9

1

2

3

7

(Not to Scale)

TSSOP

ADM8830

TOP VIEW

20

19

18

17

16

15

14

13

12

11

GND

–10VOUT

C4+

C4–

C2+

C2–

C3+

C3–

+15VOUT

CLKIN

Function

External capacitor C1 is connected between these pins. A 2.2 µF capacitor is recommended.

Positive Supply Voltage Input. Connect this pin to 3 V supply with a 2.2 µF decoupling capacitor.

Voltage Doubler Output. This is derived by doubling the 3 V supply. A 2.2 µF capacitor to

ground is required on this pin.

Voltage Regulator Input. The user has the option to bypass this circuit using the

LDO_ON/OFF pin.

+5.1 V Output Pin. This is derived by doubling and regulating the 3 V supply. A 2.2 µF ca-

pacitor to ground is required on this pin to stabilize the regulator.

+5.1 V Input Pin. This is the input to the voltage tripler and doubler inverter charge pump

circuits.

Control Logic Input. 3 V CMOS logic. A logic high selects the internal LDO for regulation of

the 5 V voltage doubler output. A logic low isolates the internal LDO from the rest of the charge

pump circuits. This allows the use of an external LDO to regulate the 5 V voltage doubler

output. The output of this LDO is then fed back into the voltage tripler and doubler/inverter

circuits of the ADM8830.

Digital Input. 3 V CMOS logic. Active low shutdown control. This shuts down the timing

generator and enables the discharge circuit to dissipate the charge on the voltage outputs,

thus driving them to 0 V.

Drive Mode Input. 3 V CMOS logic. A logic high places the part in scan (high current) mode

and the charge pump is driven by the internal oscillator. A logic low places the part in blanking

(low current) mode and the charge pump is driven by the (slower) external oscillator. This is

a power saving feature on the ADM8830.

External CLOCK Input. During a blanking period, the oscillator circuit selects this pin to drive

the charge pump circuit. This is at a lower frequency than the internal oscillator, resulting in

lower quiescent current consumption, thus saving power.

+15.3 V Output Pin. This is derived by tripling the +5.1 V regulated output. A 1 µF capacitor

is required on this pin.

External capacitor C3 is connected between these pins. A 1 µF capacitor is recommended.

External capacitor C2 is connected between these pins. A 1 µF capacitor is recommended.

External capacitor C4 is connected between these pins. A 1 µF capacitor is recommended.

–10.2 V Output Pin. This is derived by doubling and inverting the +5.1 V regulated output.

A 1 µF capacitor is required on this pin.

Device Ground Pin.

PIN FUNCTION DESCRIPTIONS

PIN CONFIGURATIONS

–4–

+5VOUT 4

LDO_IN 3

VOUT 2

+5VIN 5

V

CC

1

LFCSP

ADM8830

TOP VIEW

PIN 1

INDICATOR

15 C4–

14 C2+

13 C2–

12 C3+

11 C3–

REV. B