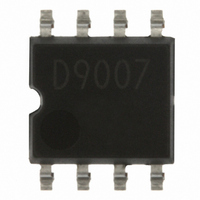

BD9007F-E2 Rohm Semiconductor, BD9007F-E2 Datasheet - Page 14

BD9007F-E2

Manufacturer Part Number

BD9007F-E2

Description

IC REG SW 2A FLEX STEPDOWN 8-SOP

Manufacturer

Rohm Semiconductor

Type

Step-Down (Buck)r

Datasheet

1.BD9006F-E2.pdf

(18 pages)

Specifications of BD9007F-E2

Internal Switch(s)

Yes

Synchronous Rectifier

No

Number Of Outputs

1

Voltage - Output

1 ~ 35 V

Current - Output

2A

Frequency - Switching

50kHz ~ 500kHz

Voltage - Input

7 ~ 35 V

Operating Temperature

-40°C ~ 105°C

Mounting Type

Surface Mount

Package / Case

8-SOP

Power - Output

690mW

Output Voltage

2. 6 V

Output Current

2 A

Input Voltage

7 V to 35 V

Operating Temperature Range

- 40 C to + 105 C

Mounting Style

SMD/SMT

Duty Cycle (max)

100 %

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

BD9007F-E2TR

●Heat Loss

SW wave from

BD9006F, BD9006HFP, BD9007F, BD9007HFP

© 2009 ROHM Co., Ltd. All rights reserved.

www.rohm.com

GND

The chip junction temperature Tj can be considered in the following two patterns:

Output

voltage

V

For thermal design, be sure to operate the IC within the following conditions.

(Since the temperatures described hereunder are all guaranteed temperature, take margin into account.)

To obtain Tj from the IC surface temperature T

< Reference value > θj-c :HRP7

To obtain Tj from the ambient temperature Ta in actual use state,Tj=T

< Reference. value >

The heat loss W of the IC can be obtained by the formula shown below:

IN

W = Ron × Io

Load

1. The ambient temperature Ta is to be 105℃ or less.

2. The chip junction temperature Tj is to be 150℃ or less.

0

Tr

0

θj-a :

θj-a :

Ron: ON resistance of IC (refer to page.4)

Vo: Output voltage

Tr: Switching rise/fall time (approximately 20nsec)

f: Oscillation frequency

DC/DC converter

controller

2

×

HRP7 89.3℃/W Single piece of IC

54.3℃/W 2-layer PCB (Copper foil area on the front side of PCB: 15×15mm

22.7℃/W 2-layer PCB (Copper foil area on the front side of PCB: 70×70mm

PCB size: 70×70×1.6mm

Copper foil area on the front side of

SOP8 222.2℃/W Single piece of IC

181.8℃/W 1-layer PCB

PCB size: 70×70×1.6mm

2

V

Vo

IN

Maximum load

T=

+ V

SOP8 32.5℃/W

1

Adequate phase margin

Inadequate phase margin

IN

V

1

f

+

+

IN:

× Icc + Tr × V

①

②

Input voltage I

V

①

②

O

Vm

7℃/W

3

3

(PCB incorporates thermal via.)

R

L

t

IN

C

<Reference>

<Procedure>

× Io × f

in actual use state, Tj=T

CC

PCB:

: Circuit current (refer to page.3)

Measurement of open loop of the DC/DC converter

To measure the open loop of the DC/DC converter, use the gain phase

analyzer or FRA to measure the frequency characteristics.

※Please contact us if you have any questions regarding phase compensation.

Furthermore, the phase margin can also be measured with the load

responsiveness. Measure variations in the output voltage when

instantaneously changing the load from no load to the maximum load. Even

though ringing phenomenon is caused, due to low phase margin, no ringing

takes place. Phase margin is provided. However, no specific phase margin

can be probed.

10.5×10.5mm

1. Check to ensure output causes no oscillation at the maximum

2. Isolate ① and ② and insert Vm

3. Measure (probe) the oscillation of ① to that of ②.

14/17

(with amplitude of approximately.100mVpp).

load inclosed loop.

Io: Load current

2

C

+θj-c×W

a

+θj-a×W

① Ron × Io

② 2 ×

=Tr × V

2

)

1

2

IN

2

2

× Tr ×

)

× Io× f

1

T

Technical Note

× V

2009.05 - Rev.A

IN

× Io