UM245R FTDI, Future Technology Devices International Ltd, UM245R Datasheet - Page 10

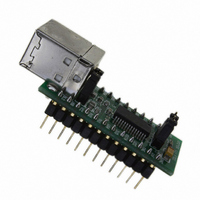

UM245R

Manufacturer Part Number

UM245R

Description

MODULE USB-PAR FIFO TTL 24-DIP

Manufacturer

FTDI, Future Technology Devices International Ltd

Datasheet

1.UM245R.pdf

(27 pages)

Specifications of UM245R

Main Purpose

Interface, USB 2.0 to Parallel FIFO Bridge

Embedded

No

Utilized Ic / Part

FT245R

Primary Attributes

300kBps to 1MBps USB to parallel FIFO via 4-Wire Interface

Secondary Attributes

Royalty-Free Drivers

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

768-1020

Pin No.

22

23

* When used in Suspend, these pins are pulled to VCCIO via internal 200kΩ resistors. These pins can be

programmed to gently pull low during USB suspend ( PWREN# = “1” ) by setting an option in the internal

EEPROM.

4.3 Jumper Configuration Options

Pin No.

1

2

3

Pin No.

1

2

Table 4.3 Jumper J2 Pin Description

© Copyright 2009 Future Technology Devices International Ltd

Table 4.1 Module Pin-Out Description

Table 4.2 Jumper J1 Pin Description

Name

TXE#

RXF#

Name

3V3

VIO

VCC

Name

USB

VCC

Type

I/O

I/O

Type

Output

PWR

PWR

Type

PWR

PWR or

Output

Description

When high, do not write data into the FIFO. When low, data can be written into the

FIFO by strobing WR high, then low. During reset this signal pin is tri-state, but pulled

up to VCCIO via an internal 200kΩ resistor. See

When high, do not read data from the FIFO. When low, there is data available in the

FIFO which can be read by strobing RD# low, then high again. During reset this signal

pin is tri-state, but pulled up to VCCIO via an internal 200kΩ resistor. See

for timing diagram.

If the Remote Wakeup option is enabled in the internal EEPROM, during USB suspend

mode (PWREN# = 1) RXF# becomes an input which can be used to wake up the USB

host from suspend mode. Strobing the pin low will cause the device to request a

resume on the USB bus.

Description

3.3V output from integrated LDO regulator. This pin is decoupled to ground on the

module PCB with a 100nF capacitor. The prime purpose of this pin is to provide the

internal 3.3V supply to the USB transceiver cell and the internal 1.5kΩ pull up resistor

on USBDP. Up to 50mA can be drawn from this pin to power external logic if required.

This pin can also be used to supply the FT245RL‟s VCCIO pin by connecting this pin to

pin 4 (VIO), or by connecting together pins 1 and 2 on jumper J1.

+1.8V to +5.25V supply to the FIFO Interface and control pins (1...3, 5, 6, 9...14, 22,

23). In USB bus powered designs connect to 3V3 to drive out at 3.3V levels (connect

jumper J1 pins 1 and 2 together), or connect to VCC to drive out at 5V CMOS level

(connect jumper J1 pins 2 and 3 together). This pin can also be supplied with an

external 1.8V - 2.8V supply in order to drive out at lower levels. It should be noted that

in this case this supply should originate from the same source as the supply to Vcc.

This means that in bus powered designs a regulator which is supplied by the 5V on the

USB bus should be used.

VCC Output. This will be 5V from the USB bus if pins 1 and 2 on jumper J2 are

connected. Alternatively, if the module is in a self powered configuration, the supply to

the VCC module pins (15 and 21) will be brought out to this jumper pin.

Connect this jumper J1 pin 2 in order to supply the device IO pins from the supply to

VCCIO.

Description

5V Power output USB port. For a low power USB bus powered design, up to 100mA can

be sourced from the 5V supply on the USB bus. A maximum of 500mA can be sourced

from the USB bus in a high power USB bus powered design with the use of an external

power switch (See Section 7.3).

Board supply input. Connect to jumper J2 pin 1 in order to supply the board from the

USB bus.

This pin is internally connected to the VCC DIP pins. Remove the jumper connector in a

self powered design.

UM245R USB - Parallel FIFO Development Module Datasheet Version 1.04

Document Reference No.: FT_000202

Section 4.4

Clearance No.: FTDI# 124

for timing diagram.

Section 4.4

9