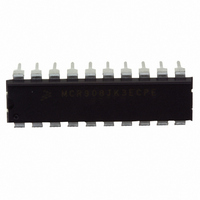

MCR908JK3ECPE Freescale Semiconductor, MCR908JK3ECPE Datasheet - Page 119

MCR908JK3ECPE

Manufacturer Part Number

MCR908JK3ECPE

Description

IC MCU FLASH 8BIT RC OSC 20-DIP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908JK1ECDWE.pdf

(180 pages)

Specifications of MCR908JK3ECPE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Peripherals

LED, LVD, POR, PWM

Number Of I /o

15

Program Memory Size

4KB (4K x 8)

Program Memory Type

FLASH

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.3 V

Data Converters

A/D 12x8b

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

20-DIP (0.300", 7.62mm)

Processor Series

HC08JK

Core

HC08

Data Bus Width

8 bit

Data Ram Size

128 B

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

15

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

Through Hole

Development Tools By Supplier

FSICEBASE, DEMO908JL16E, M68CBL05CE

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 12 Channel

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Connectivity

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MCR908JK3ECPE

Manufacturer:

Freescale

Quantity:

289

The vector fetch or software clear and the return of all enabled keyboard interrupt pins to 1 may occur in

any order.

If the MODEK bit is clear, the keyboard interrupt pin is falling-edge-sensitive only. With MODEK clear, a

vector fetch or software clear immediately clears the keyboard interrupt request.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a

keyboard interrupt pin stays at 0.

The keyboard flag bit (KEYF) in the keyboard status and control register can be used to see if a pending

interrupt exists. The KEYF bit is not affected by the keyboard interrupt mask bit (IMASKK) which makes

it useful in applications where polling is preferred.

To determine the logic level on a keyboard interrupt pin, disable the pull-up device, use the data direction

register to configure the pin as an input and then read the data register.

12.4.1 Keyboard Initialization

When a keyboard interrupt pin is enabled, it takes time for the internal pull-up to reach a logic 1. Therefore

a false interrupt can occur as soon as the pin is enabled.

To prevent a false interrupt on keyboard initialization:

An interrupt signal on an edge-triggered pin can be acknowledged immediately after enabling the pin. An

interrupt signal on an edge- and level-triggered interrupt pin must be acknowledged after a delay that

depends on the external load.

Another way to avoid a false interrupt:

12.5 Keyboard Interrupt Registers

Two registers control the operation of the keyboard interrupt module:

Freescale Semiconductor

1. Mask keyboard interrupts by setting the IMASKK bit in the keyboard status and control register.

2. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

3. Write to the ACKK bit in the keyboard status and control register to clear any false interrupts.

4. Clear the IMASKK bit.

1. Configure the keyboard pins as outputs by setting the appropriate DDRA bits in the data direction

2. Write 1s to the appropriate port A data register bits.

3. Enable the KBI pins by setting the appropriate KBIEx bits in the keyboard interrupt enable register.

•

•

register A.

Keyboard status and control register

Keyboard interrupt enable register

Setting a keyboard interrupt enable bit (KBIEx) forces the corresponding

keyboard interrupt pin to be an input, overriding the data direction register.

However, the data direction register bit must be a 0 for software to read the

pin.

MC68HC908JL3E Family Data Sheet, Rev. 4

NOTE

Keyboard Interrupt Registers

119