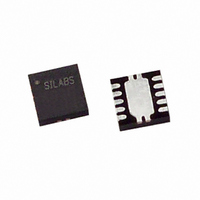

C8051F305-GMR Silicon Laboratories Inc, C8051F305-GMR Datasheet - Page 151

C8051F305-GMR

Manufacturer Part Number

C8051F305-GMR

Description

IC 8051 MCU 2K FLASH 11QFN

Manufacturer

Silicon Laboratories Inc

Series

C8051F30xr

Specifications of C8051F305-GMR

Core Processor

8051

Core Size

8-Bit

Speed

25MHz

Connectivity

SMBus (2-Wire/I²C), UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

8

Program Memory Size

2KB (2K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 3.6 V

Oscillator Type

External

Operating Temperature

-40°C ~ 85°C

Package / Case

11-VQFN

For Use With

336-1444 - ADAPTER PROGRAM TOOLSTICK F300

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Data Converters

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

C8051F305-GMR

Manufacturer:

SILICONLABS/芯科

Quantity:

20 000

15.2. Timer 2

Timer 2 is a 16-bit timer formed by two 8-bit SFRs: TMR2L (low byte) and TMR2H (high byte). Timer 2 may

operate in 16-bit auto-reload mode or (split) 8-bit auto-reload mode. The T2SPLIT bit (TMR2CN.3) defines

the Timer 2 operation mode.

Timer 2 may be clocked by the system clock, the system clock divided by 12, or the external oscillator

source divided by 8. The external clock mode is ideal for real-time clock (RTC) functionality, where the

internal oscillator drives the system clock while Timer 2 (and/or the PCA) is clocked by an external preci-

sion oscillator. Note that the external oscillator source divided by 8 is synchronized with the system clock.

15.2.1. 16-bit Timer with Auto-Reload

When T2SPLIT (TMR2CN.3) is zero, Timer 2 operates as a 16-bit timer with auto-reload. Timer 2 can be

clocked by SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. As the

16-bit timer register increments and overflows from 0xFFFF to 0x0000, the 16-bit value in the Timer 2

reload registers (TMR2RLH and TMR2RLL) is loaded into the Timer 2 register as shown in Figure 15.4,

and the Timer 2 High Byte Overflow Flag (TMR2CN.7) is set. If Timer 2 interrupts are enabled (if IE.5 is

set), an interrupt will be generated on each Timer 2 overflow. Additionally, if Timer 2 interrupts are enabled

and the TF2LEN bit is set (TMR2CN.5), an interrupt will be generated each time the lower 8 bits (TMR2L)

overflow from 0xFF to 0x00.

External Clock / 8

SYSCLK / 12

SYSCLK

T2XCLK

0

1

Figure 15.4. Timer 2 16-Bit Mode Block Diagram

M

T

2

H

CKCON

M

T

2

L

0

1

M

T

1

M

T

0

S

C

A

1

C

S

A

0

TR2

TCLK

Rev. 2.9

Overflow

TMR2L

TMR2RLL TMR2RLH

TMR2L

To SMBus

TMR2H

C8051F300/1/2/3/4/5

Reload

To ADC,

SMBus

T2SPLIT

TF2LEN

T2XCLK

TF2H

TF2L

TR2

Interrupt

151