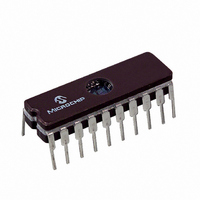

PIC16C782/JW Microchip Technology, PIC16C782/JW Datasheet

PIC16C782/JW

Specifications of PIC16C782/JW

Available stocks

Related parts for PIC16C782/JW

PIC16C782/JW Summary of contents

Page 1

... CMOS Microcontrollers with A/D, D/A, OPAMP, Comparators and PSMC 2001 Microchip Technology Inc. PIC16C781/782 Data Sheet Preliminary DS41171A ...

Page 2

... Serialized Quick Term Programming (SQTP service mark of Microchip Technology Incorporated in the U.S.A. All other trademarks mentioned herein are property of their respective companies. © 2001, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved. Printed on recycled paper. Microchip received QS-9000 quality system ...

Page 3

... Four user programmable ID locations • Wide operating voltage range: - 2.5V to 5.5V for commercial and industrial temperature ranges - Extended temperature range available 2001 Microchip Technology Inc. PIC16C781/782 Microcontroller Core Features (Continued): • Low power, high speed CMOS EPROM technology • Fully static design • ...

Page 4

... PIC16C781 MHz POR, BOR, MCLR, WDT (PWRT, OST) POR, BOR, MCLR, WDT (PWRT, OST) 1K 128 Input only External, 2 Internal (AN<7:4> Yes Yes 35 Instructions Preliminary PIC16C782 MHZ 2K 128 Input only External, 2 Internal (AN<7:4> Yes Yes 35 Instructions 2001 Microchip Technology Inc. ...

Page 5

... When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include liter- ature number) you are using. Customer Notification System Register on our web site at www.microchip.com/cn to receive the most current information on all of our products. 2001 Microchip Technology Inc. PIC16C781/782 Preliminary DS41171A-page 3 ...

Page 6

... PIC16C781/782 NOTES: DS41171A-page 4 Preliminary 2001 Microchip Technology Inc. ...

Page 7

... Note 1: AV and AV pins are used by the following modules: C1, C2, OPA, DAC, ADC, and 2001 Microchip Technology Inc. PIC16C781/782 manual is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules. This data sheet covers two devices: PIC16C781 and PIC16C782 ...

Page 8

... W reg Timer1 (TMR1) Voltage Reference Module ( Comparator 8-bit ADC C2 8-bit OPAMP OPA DAC Preliminary RA0/AN0/OPA+ RA1/AN1/OPA- RA2/AN2/V 2 REF RA3/AN3/V 1 REF RA4/T0CKI RA5/MCLR/V PP RA6/OSC2/CLKOUT/T1CKI RA7/OSC1/CLKIN RB0/INT/AN4/V R RB1/AN5/VDAC RB2/AN6 RB3/AN7/OPA RB4 RB5 RB6/C1/PSMC1A RB7/C2/PSMC1B/T1G ( Programmable Low Voltage Detect PLVD . R 2001 Microchip Technology Inc. ...

Page 9

... RB1/AN5/V DAC RB2/AN6 RB3/AN7/OPA DAC AN4 AN5 AN6 AN7 V 1 REF V DAC AN4 AN5 AN6 AN7 V 2 REF V DAC DARS<1:0> REF N/C 3 2001 Microchip Technology Inc. PIC16C781/782 OPAON VCFG<1:0> CMPEN GBWP AV DD CHS<2:0> REF DAC ADON 6 GO/DONE EN 7 CHS3 REFERENCE 1 VREN ...

Page 10

... ADC, Comparator Input — TTL CMOS Bi-directional I/O AN ADC, Comparator Input — AN OPAMP Output — TTL CMOS Bi-directional I/O TTL CMOS Bi-directional I/O TTL CMOS Bi-directional I/O CMOS Comparator 1 Output — CMOS PSMC Output 1A — Preliminary Description 2001 Microchip Technology Inc. ...

Page 11

... T1G Legend Schmitt Trigger AN = Analog XTAL = Crystal CMOS = CMOS Output 2001 Microchip Technology Inc. PIC16C781/782 Input Output Type Type TTL CMOS Bi-directional I/O — CMOS Comparator 2 Output CMOS PSMC Output 1B — ST Timer 1 Gate Input — Power — Positive Supply for Analog Power — ...

Page 12

... PIC16C781/782 NOTES: DS41171A-page 10 Preliminary 2001 Microchip Technology Inc. ...

Page 13

... RETFIE, RETLW Stack Level 1 Stack Level 2 Stack Level 8 RESET Vector Interrupt Vector On-Chip Program Page 0 Memory 2001 Microchip Technology Inc. PIC16C781/782 FIGURE 2-2: CALL, RETURN RETFIE, RETLW On-Chip Program Memory 2.2 Data Memory Organization 0000h The data memory is partitioned into multiple banks, which contain the General Purpose Registers and the Special Function Registers ...

Page 14

... Bank 3 2001 Microchip Technology Inc. ...

Page 15

... The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are trans- ferred to the upper byte of the program counter. See Section 2.9 for more detail. 2: These registers can be addressed from any bank. 2001 Microchip Technology Inc. PIC16C781/782 2.2.2 SPECIAL FUNCTION REGISTERS ...

Page 16

... LV1 LV0 66 --00 0101 25 1111 1111 — — — — 71 --00 ---- 2001 Microchip Technology Inc. ...

Page 17

... The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are trans- ferred to the upper byte of the program counter. See Section 2.9 for more detail. 2: These registers can be addressed from any bank. 2001 Microchip Technology Inc. Bit 5 Bit 4 Bit 3 ...

Page 18

... Microchip Technology Inc. ...

Page 19

... Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. PIC16C781/782 For example, CLRF STATUS clears the upper three bits and sets the Z bit. This leaves the STATUS register as 000u u1uu (where u = unchanged). ...

Page 20

... T0CS T0SE PSA (1) /4) OSC TMR0 Rate WDT Rate 128 1 : 128 1 : 256 W = Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary R/W-1 R/W-1 R/W-1 PS2 PS1 PS0 bit0 x = Bit is unknown 2001 Microchip Technology Inc. ...

Page 21

... Note 1: Individual RB pin interrupt-on-change can be enabled/disabled from the Interrupt- on-Change PORTB register (IOCB). Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit, GIE (INTCON< ...

Page 22

... Register 2-3). R/W-0 R/W-0 U-0 ADIE C2IE C1IE — Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary U-0 U-0 R/W-0 — — TMR1IE bit0 x = Bit is unknown 2001 Microchip Technology Inc. ...

Page 23

... TMR1IF: TMR1 Overflow Interrupt Flag bit 1 = TMR1 register overflowed (must be cleared in software TMR1 register did not overflow Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. PIC16C781/782 Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit, GIE (INTCON< ...

Page 24

... WDTON OSCF W = Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary Typical Time Inactive Minimum Maximum 100 s 300 s 1.25 s 3.25 s U-0 R/W-q R/W-q — POR BOR bit Bit is unknown 2001 Microchip Technology Inc. ...

Page 25

... After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on). 2001 Microchip Technology Inc. PIC16C781/782 2.11 INDF The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer) ...

Page 26

... TMR1IF 0000 ---0 0000 ---0 PS1 PS0 xxxx xxxx 1111 1111 DC C 0001 1xxx 000q quuu INTF RBIF 0000 000x 0000 000u — TMR1IE 0000 ---0 0000 ---0 POR BOR ---q 1-qq ---q 1-qq 2001 Microchip Technology Inc. ...

Page 27

... TRIS bit should be set to input mode when using pins as analog inputs. Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. PIC16C781/782 to prevent unnecessary current drawn from the power supply. The Analog Select register (ANSEL) allows the user to individually select the Digital/Analog mode on these pins ...

Page 28

... I/O PORTA ; Select Bank 0 PORTA ; Preset PORTA data ; reg TRISA ; Select Bank 1 B’00001111’; Digital I/O ; config data TRISA ; Configure PORTA ; digital B’00000011’; Analog I/O config ; data ANSEL ; Configure PORTA ; analog use pin RA6/OSC2/CLKOUT/ 2001 Microchip Technology Inc. ...

Page 29

... FIGURE 3-1: BLOCK DIAGRAM OF RA0/AN0/OPA+ PIN RD ANSEL RD TRISA Data Bus ANSEL Reg ANSEL CK RD PORTA Analog Function Enable AN0/OPA+ (see Figure 1-3) ANSEL<0> 2001 Microchip Technology Inc. PIC16C781/782 Data Reg TRISA<0> FUNCTION PORTA<0> READ x Digital In Pin x Analog In 0 Preliminary V DD RA0/AN0/OPA+ ...

Page 30

... FIGURE 3-2: BLOCK DIAGRAM OF RA1/AN1/OPA- PIN RD ANSEL RD TRISA Data Bus ANSEL Reg ANSEL CK RD PORTA Analog Function Enable AN1/OPA- (see Figure 1-3) ANSEL<1> DS41171A-page Data Reg TRISA<1> FUNCTION PORTA<1> READ x Digital In Pin x Analog In 0 Preliminary V DD RA1/AN1/OPA 2001 Microchip Technology Inc. ...

Page 31

... BLOCK DIAGRAM OF RA2/AN2/V RD ANSEL Data Bus Data Reg PORTA CK TRIS Reg TRISA CK RD TRISA ANSEL Reg ANSEL CK RD PORTA Analog Function Enable AN2/V 2 (see Figure 1-3) REF ANSEL<2> 2001 Microchip Technology Inc. PIC16C781/782 2 PIN REF Data Reg TRISA<2> FUNCTION PORTA<2> READ 1 Digital In ...

Page 32

... RD TRISA ANSEL Reg ANSEL CK RD PORTA Analog Function Enable AN3/V 1 (see Figure 1-3) REF ANSEL<3> DS41171A-page 30 1 PIN REF Data Reg TRISA<3> FUNCTION PORTA<3> READ 1 Digital In 0 Digital Out x Analog In Preliminary V DD RA3/AN3/V 1 REF V SS Pin Pin 0 2001 Microchip Technology Inc. ...

Page 33

... FIGURE 3-5: BLOCK DIAGRAM OF RA4/T0CKI PIN Data Reg. Data Bus D WR PORTA CK TRIS Reg TRISA CK RD TRISA RD PORTA TMR0 Clock Input TRISA<4> 2001 Microchip Technology Inc Vss Q Data Reg PORTA<4> FUNCTION PORTA<4> READ x Digital In Pin 0 0 Output Pin 1 Hi-Z Output Pin ...

Page 34

... MCLRE To MCLR Circuit Program Mode Data Bus RD TRISA RD PORTA MCLRE Internal External Note 1: See Configuration Word <5>, Register 14-1. DS41171A-page 32 PIN PP MCLR Filter HV Detect V SS Data Reg (1) TRISA<5> FUNCTION PORTA<5> READ x Digital In x MCLR Preliminary RA5/MCLR Pin 0 2001 Microchip Technology Inc. ...

Page 35

... T1CKI (1) OSC MODE TMR1 OSCILLATOR LP, XT, HS RC, INTRC w/ CLKOUT INTRC w/o CLKOUT INTRC w/o CLKOUT RC w/o CLKOUT EC N/A = Not Available w/ = with Note 1: See Configuration Word F 2001 Microchip Technology Inc. OSC1 Oscillator Circuit (1) F <2:0> OSC T1OSCEN (INTRC w/o CLKOUT) or (RC w/o CLKOUT) or (EC) ...

Page 36

... RA4 RA3 RA2 RA1 RA0 AN4 AN3 AN2 AN1 AN0 Preliminary V DD RA7/OSC1/CLKIN EC Mode V SS PORTA<7> READ Pin Value on: Value on all POR, BOR other RESETS xxxx 0000 uuuu 0000 1111 1111 1111 1111 1111 1111 1111 1111 2001 Microchip Technology Inc. ...

Page 37

... DAC. When the pin is used as an analog I/O, the ANSEL register must have bit 5 set to configure the RB1 pin as an analog I/O. 2001 Microchip Technology Inc. PIC16C781/782 Pin RB2 is multiplexed with the analog function ADC/ Comparator Input AN6. When the pin is used as an analog input, the ANSEL register must have bit 6 to select the Analog mode for the pin ...

Page 38

... There are specific cases in which the functions of the TRISB and ANSEL regis- ters can be overridden by a peripheral or configuration through Figure 3-16 for details). Preliminary R/W-1 R/W-1 WPUB1 WPUB0 bit0 x = Bit is unknown R/W-0 R/W-0 IOCB1 IOCB0 bit0 x = Bit is unknown word (see Figure 3-9 2001 Microchip Technology Inc. ...

Page 39

... TRIS Reg TRISB TRISB ANSEL Reg ANSEL ANSEL IOCB Reg Set RBIF WR IOCB IOCB RD PORTB INT Input Analog Function Enable AN4/V R VREN & VROE ANSEL<4> 2001 Microchip Technology Inc. PIC16C781/782 PIN R V Output RBPU ... Q D From other EN RB<7:0> pins TRISB<0> FUNCTION 0 1 ...

Page 40

... DAON & DAOE ANSEL<5> DS41171A-page 38 PIN DAC V Output DAC RBPU Set RBIF ... Q From other RB<7:0> pins TRISB<1> FUNCTION 0 1 Digital Digital Out 1 x Analog Analog Out Preliminary V DD Weak P Pull- RB1/AN5/V DAC V SS TTL PORTB<1> READ Pin Pin 0 0 2001 Microchip Technology Inc. ...

Page 41

... CK Q TRIS Reg TRISB TRISB ANSEL Reg ANSEL ANSEL IOCB Reg IOCB IOCB RD PORTB Analog Function Enable AN6 ANSEL<6> 2001 Microchip Technology Inc. RBPU Set RBIF ... Q From other RB<7:0> pins TRISB<2> FUNCTION PORTB<2> READ 1 Digital In 0 Digital Out x Analog In Preliminary PIC16C781/782 ...

Page 42

... Analog HI internal drive on pin (analog input) during calibration. DS41171A-page 40 OPA Output RBPU ... Q D From other EN RB<7:0> pins ANSEL<7> ADC/C1/C2 INPUT FUNCTION 0 Digital Digital I/O 1 Analog Analog In 1 Analog OPA Output 1 Analog HI-Z Calibration Preliminary V DD Weak P Pull- RB3/AN7/OPA V SS TTL Q1 Q3 PORTB<3> READ Pin 2001 Microchip Technology Inc. ...

Page 43

... FIGURE 3-13: BLOCK DIAGRAM OF RB4 PIN WPUB Reg. Data Bus D WR WPUB CK RD WPUB PORTB Reg PORTB CK TRIS Reg TRISB CK RD TRISB RD IOCB IOCB Reg IOCB CK RD PORTB TRISB<4> 2001 Microchip Technology Inc RBPU Set RBIF ... Q From other RB<7:0> pins FUNCTION PORTB< ...

Page 44

... D WR PORTB CK TRIS Reg TRISB CK RD TRISB RD IOCB IOCB Reg IOCB CK RD PORTB TRISB<5> DS41171A-page RBPU Set RBIF ... Q From other RB<7:0> pins FUNCTION PORTB<5> READ 0 Digital Out Pin 1 Digital In Pin Preliminary V DD Weak P Pull- RB5 V SS TTL 2001 Microchip Technology Inc. ...

Page 45

... RD WPUB Data Reg PORTB CK Q TRIS Reg TRISB TRISB RD PORTB RD IOCB IOCB Reg IOCB CK Q Serial Programming Clock PSMC SMCON COMPARATOR C1OE 2001 Microchip Technology Inc. RBPU Q Set RBIF Q From other RB<7:0> pins PORTB TRISB<6> Preliminary PIC16C781/782 V DD Weak Pull- RB6/C1/PSMC1A N ...

Page 46

... SMCON SMCOM DS41171A-page 44 C2OE SCEN SMCOM SMCON V DD RBPU Weak Pull-up P C2OUT PSMC1B SC Switch COMPARATOR PORTB TRISB<7> C2OE SCEN Preliminary V DD RB7/C2/PSMC1B/T1G TTL Q1 RD Port Q3 FUNCTION 1 Digital In 0 Digital Out 0 Digital Out 0 C2OUT 0 C2OUT 0 Slope Compensation 0 PSMC1B 2001 Microchip Technology Inc. ...

Page 47

... WPUB PORTB Weak Pull-up Control 96h IOCB PORTB Interrupt-on-Change Control 9Dh ANSEL AN7 Legend unknown unchanged unimplemented, read as ’0’. Shaded cells are not used by PORTB. 2001 Microchip Technology Inc. Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 RB6 RB5 RB4 RB3 ...

Page 48

... PIC16C781/782 NOTES: DS41171A-page 46 Preliminary 2001 Microchip Technology Inc. ...

Page 49

... The value of the program memory word pointed to by PMADRH and PMADRL after a program memory read command. Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. 3FFFh. When the device contains less memory than the full address range of the PMADRH:PMARDL regis- ters, the Most Significant bits of the PMADRH register are ignored. ...

Page 50

... U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary R/W-0 R/W-0 R/W-0 PMD2 PMD1 PMD0 bit0 x = Bit is unknown R/W-x R/W-x R/W-x PMA10 PMA9 PMA8 bit0 x = Bit is unknown R/W-x R/W-x R/W-x PMA2 PMA1 PMA0 bit0 x = Bit is unknown 2001 Microchip Technology Inc. ...

Page 51

... Get LSB of word MOVWF PROG_DATA_LO MOVF PMDATH,W ; Get MSB of word MOVWF PROG_DATA_HI 2001 Microchip Technology Inc. PIC16C781/782 in the following instructions. PMDATH and PMDATL registers hold this value until another read or until RESET. bit RD Note 1: Interrupts must be disabled during the time from setting PMCON1<0> (RD) to the second instruction thereafter ...

Page 52

... Bit 0 all other POR, BOR RESETS PMD1 PMD0 0000 0000 0000 0000 PMA1 PMA0 xxxx xxxx uuuu uuuu PMD9 PMD8 --00 0000 --00 0000 PMA9 PMA8 ---x xxxx ---u uuuu — RD 1--- ---0 1--- ---0 PC+4 PC+5 INSTR(PC+3) INSTR(PC+4) Executed here Executed here 2001 Microchip Technology Inc. ...

Page 53

... T0CS Note 1: T0CS, T0SE, PSA, PS<2:0> (OPTION_REG<5:0>). 2: The prescaler is shared with Watchdog Timer (refer to Figure 5-2 for detailed block diagram). 2001 Microchip Technology Inc. When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal system clock ...

Page 54

... TMR0 interrupt cannot awaken the processor from SLEEP, since the timer is shut-off during SLEEP. 5.4 Effects of RESET A device RESET will program Timer0 for an external CLRF TMR0, clock input on RA4/T0CKI, Hi-Low edge, and no pres- caler. The TMR0 register is not cleared. Preliminary 2001 Microchip Technology Inc. ...

Page 55

... Address Name Bit 7 01h,101h TMR0 Timer0 Register 0Bh,8Bh, INTCON GIE 10Bh,18Bh 81h,181h OPTION_REG RBPU INTEDG Legend unknown unchanged unimplemented, read as ’0’. Shaded cells are not used by Timer0. 2001 Microchip Technology Inc Sync with 1 Internal 0 Clocks (2 T Delay) CY PSA 8-bit Prescaler MUX PS< ...

Page 56

... PIC16C781/782 NOTES: DS41171A-page 54 Preliminary 2001 Microchip Technology Inc. ...

Page 57

... INTRC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source. Note 1: In Counter mode, the counter increments on the rising edge of the clock. 2001 Microchip Technology Inc. PIC16C781/782 EXAMPLE 6-1: TIMER1 INITIALIZATION ;* This code block will configure Timer1 for ...

Page 58

... Available prescaler values are: T1CKPS<1:0> Bit /4. OSC Note: To use the LP oscillator as the Timer1 oscillator: 1. TMR1CS must be set. 2. T1OSCEN must be set. 3. The Configuration Word must select INTRC w/o CLKOUT. Preliminary Prescaler Value Bit 0 1 1:8 0 1:4 1 1:2 0 1:1 2001 Microchip Technology Inc. ...

Page 59

... TMR1CS: Timer1 Clock Source Select bit 1 = External clock from pin RA6/OSC2/CLKOUT/T1CKI (on the rising edge Internal clock (F bit 0 TMR1ON: Timer1 On bit 1 = Enables Timer1 0 = Stops Timer1 Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. PIC16C781/782 R/W-0 R/W-0 R/W-0 T1OSCEN /4) OSC W = Writable bit U = Unimplemented bit, read as ‘0’ ...

Page 60

... RA7/OSC1/CLKIN RA6/OSC2/ CLKOUT/ T1CKI INTRC w/o CLKOUT Mode T1OSCEN LPEN DS41171A-page Comparator Module TMR1 Clock 0 TMR1L 1 T1SYNC 1 Prescaler OSC Internal 0 Clock 2 T1CKPS<1:0> TMR1CS Preliminary RB7/C2/ TMR1ON PSMC1B/T1G TMR1GE TMR1ON TMR1GE Synchronized Clock Input Synchronize det SLEEP Input 2001 Microchip Technology Inc. ...

Page 61

... T1CON — TMR1GE T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON -000 0000 -uuu uuuu Legend unknown unchanged unimplemented, read as '0'. Shaded cells are not used by Timer1. 2001 Microchip Technology Inc. 6.4 Timer1 Interrupt The TMR1 register pair (TMR1H and TMR1L) incre- ments from 0000h to FFFFh and then rolls over to 0000h. When Timer1 rolls over, the TMR1IF bit (PIR1< ...

Page 62

... PIC16C781/782 NOTES: DS41171A-page 60 Preliminary 2001 Microchip Technology Inc. ...

Page 63

... Bit 7 Bit 6 Bit 5 09Bh REFCON — — 2001 Microchip Technology Inc. Setting the VREN flag (REFCON<3>), enables the module. Following initial start-up, the module should be allowed to stabilize for best accuracy. See Section 17.0 for information concerning stabilization times and conditions. To route the reference voltage to the external RB0/INT/ AN4/V pin, the VROE flag (REFCON< ...

Page 64

... PIC16C781/782 NOTES: DS41171A-page 62 Preliminary 2001 Microchip Technology Inc. ...

Page 65

... V and Vss. Clearing LVDEN will disable DD the module and disconnect the resistor ladder from Vss. 2001 Microchip Technology Inc. condition. The time between T to the microcontroller for completing a ‘graceful’ power- down before V Figure 8 simplified block diagram for the PLVD ...

Page 66

... The bandgap reference is also enabled by other modules within the PIC16C781/782 as part of their operation. Other modules using the bandgap include the following: • V module R • BOR module • OPA calibration module PLVD Control Register Internally Generated Reference Voltage Preliminary LVDIF 2001 Microchip Technology Inc. ...

Page 67

... Internally Generated Reference Stable CASE LVDIF Enable LVD Internally Generated Reference Stable 2001 Microchip Technology Inc. PIC16C781/782 2. Ensure that PLVD interrupts are disabled (the LVDIE bit is cleared, or the GIE bit is cleared). 3. Enable the PLVD module (set the LVDEN bit in the LVDCON register). 4. ...

Page 68

... Value at POR DS41171A-page 66 U-0 R-0 R/W-0 R/W-0 — BGST LVDEN LV3 W = Writable bit U = Unimplemented bit, read as ‘0’ ‘1’ = Bit is set ‘0’ = Bit is cleared Preliminary R/W-1 R/W-0 R/W-1 LV2 LV1 LV0 bit Bit is unknown 2001 Microchip Technology Inc. ...

Page 69

... LVDCON — — BGST 08Ch PIE1 LVDIE ADIE 08Ch PIR1 LVDIF ADIF 2001 Microchip Technology Inc. ; Select Bank 1 ; Disable PLVD interrupt ; Enable PLVD, 4.2-4.4V trip ; ; ; Select Bank 0 ; Clear PLVD interrupt flag ; Select Bank 0 ; Test for PLVD trip ; If tripped save 4 pwrfail 8.4 ...

Page 70

... PIC16C781/782 NOTES: DS41171A-page 68 Preliminary 2001 Microchip Technology Inc. ...

Page 71

... REF RB0/INT/AN4/V R RB1/AN5/V DAC RB2/AN6 RB3/AN7/OPA 2001 Microchip Technology Inc. PIC16C781/782 tures a snapshot of the voltage and holds it for the ADC. The ADC then generates the 8-bit result via suc- cessive approximation. The analog reference voltage (ADC selectable from the following options: • ...

Page 72

... Reserved. Do not use. 101 = Reserved. Do not use. 110 = Reserved. Do not use. 111 = Reserved. Do not use Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary R/W-0 R/W-0 CHS3 ADON bit Bit is unknown 2001 Microchip Technology Inc. ...

Page 73

... V DAC bit 3-0 Unimplemented: Read as ’0’ Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. 9.1.3 ADRES REGISTER The ADRES register, shown in Register 9-2, contains the 8-bit result of the conversion. At the completion of the ADC conversion: voltage • 8-bit result is loaded into ADRES. ...

Page 74

... ADC clock source selected. Device Frequency 20 MHz 5 MHz (2) (2) 100 ns 400 ns 400 ns 1.6 s 1.6 s 6.4 s (1,4) (1, time time. AD Preliminary . The REF ) R 1) REF ) DAC ) VDD input, REF . The source AD time AD times AD 1.25 MHz 333.33kHz 1 (3) 6 (3) (3) 25 (1,4) ( 2001 Microchip Technology Inc. ...

Page 75

... Given (ADC /512), for 1/2LSb resolution HOLD REF The above equation reduces to -(51.2 pF)( Ln(1/511) CAP SS S 2001 Microchip Technology Inc. Example 9-1 shows the calculation of the minimum required acquisition time T based on the following system assumptions 51.2 pF HOLD R = 10k S 1/2 LSb error ...

Page 76

... ADCON1 ; Select Bank 1 ADCON1 ; AVDD as VREF TRISA,0 ; Set RA0 as input ANSEL,0 ; Set RA0 as analog ADCON0 ; Select Bank0 B’11000001’ ADCON0 ; RC ADC on ADCON0 ; Select Bank 0 ADCON0,GO ; Start convert ADCON0,GO ; Test for end ADC_CN_LOOP ; If not, wait ADRES,W ; Get result 2001 Microchip Technology Inc. ...

Page 77

... A/D clock source must be set to RC (ADCS1:ADCS0 = 11). To perform an ADC conversion in SLEEP, ensure the SLEEP instruction immediately follows the instruc- tion that sets the GO/DONE bit. 2001 Microchip Technology Inc. PIC16C781/782 9.6 ADC Accuracy/Error The absolute accuracy (absolute error) specified for the ADC converter includes the sum of all contributions for: • ...

Page 78

... A good reference for ADC converters is the "Analog- Digital Conversion Handbook" third edition, published by Prentice Hall (ISBN 0-13-03-2848-0). FIGURE 9-3: FFh FEh 04h 03h 02h 01h 00h Preliminary /256 (Figure 9-3). REF ADC TRANSFER FUNCTION Analog Input Voltage 2001 Microchip Technology Inc. ...

Page 79

... PORTA RA7 RA6 06h PORTB RB7 RB6 9Dh ANSEL Analog Channel Select Legend unknown unchanged unimplemented, read as '0'. Shaded cells are not used for ADC conversion. 2001 Microchip Technology Inc. Yes Finish Conversion SLEEP Instruction ADIF = Wake-up Finish Conversion SLEEP? ...

Page 80

... PIC16C781/782 NOTES: DS41171A-page 78 Preliminary 2001 Microchip Technology Inc. ...

Page 81

... DA<7:0>: Digital-to-Analog Converter Digital Input bits Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. 10.1 Control Registers The DAC module is controlled via two special function registers: DACON0 and DAC. The DACON0 register, shown in Register 10-1: • Enables DAC • ...

Page 82

... To enable the DAC output as a reference for the Comparator module, C1R/C2R bits DAOE bit (CM1CON0<2>/CM2CON0<2>) must be set. DAON DAC EN REF DAC DAC Register Converter 8 Preliminary DAOE & DAON V pin DAC V DAC Voltage for ADC and Comparators Reference 2001 Microchip Technology Inc. ...

Page 83

... DAC DA7 DA6 86h TRISB RB7 RB6 9Dh ANSEL AN7 AN6 Legend unknown unchanged unimplemented, read as '0'. Shaded cells are not used for DAC conversion. 2001 Microchip Technology Inc. PIC16C781/782 FIGURE 10- FFh FEh 04h 03h 02h 01h 00h Offset error measures the first actual transition of a code versus the first ideal transition of a code ...

Page 84

... PIC16C781/782 NOTES: DS41171A-page 82 Preliminary 2001 Microchip Technology Inc. ...

Page 85

... Register 11-2, controls the Automatic Calibration Module. FIGURE 11-1: OPA MODULE BLOCK DIAGRAM RA0/AN0/OPA+ RA1/AN1/OPA- RB3/AN7/OPA 2001 Microchip Technology Inc. PIC16C781/782 11.1.1 OPACON REGISTER The OPA module is enabled by setting the OPAON bit (OPACON<7>). When enabled, the OPA forces the output driver of RB3/AN7/OPA into tri-state to prevent contention between the driver and the OPA output. Clearing the CMPEN bit (OPACON,6> ...

Page 86

... OPAMP stability. 4: When using the DAC as a reference for calibration, CALREF = 1 (CALCON<5>), the V ified common mode voltage for the OPAMP. Preliminary U-0 U-0 R/W-0 — — — GBWP bit Bit is unknown voltage must be within the spec- DAC 2001 Microchip Technology Inc. ...

Page 87

... V set to desired common voltage reference DAC 0 = 1.2V nominal source (internal voltage source) Note: V DAC bit 4-0 Reserved: Do not use Legend Cleared by hardware R = Readable bit - n = Value at POR 2001 Microchip Technology Inc OPA 1 Automatic Calibration Module R-0 R/W-0 U-0 U-0 CALREF — — ...

Page 88

... DC and falls off with frequency. Gain Bandwidth Product or GBWP is the frequency at which the open loop gain falls off to 0 dB. The lower GBWP is optimized for systems requiring low fre- quency response and low power consumption. Preliminary -1.4V, or below 0V, are not 2001 Microchip Technology Inc. ...

Page 89

... PORTA Data Direction Register 11Eh DAC DA7 DA6 11Fh DACON0 DAON DAOE Legend unknown unchanged unimplemented, read as '0'. Shaded cells are not used for the OPA module. 2001 Microchip Technology Inc. PIC16C781/782 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 — — — — — ...

Page 90

... PIC16C781/782 NOTES: DS41171A-page 88 Preliminary 2001 Microchip Technology Inc. ...

Page 91

... AN<7:4>. Note: To use AN<7:4> as analog inputs, the appropriate bits must be programmed in the ANSEL register. 2001 Microchip Technology Inc. PIC16C781/782 Setting C1R (CM1CON0<2>) selects the output of the DAC module as the reference voltage for the compara- tor. Clearing C1R selects the V AN3/V 1 pin ...

Page 92

... C2VP RB2/AN6 2 RB3/AN7/OPA 3 C2R RA2/AN2/V 2 REF DAC DS41171A-page 90 To Interrupt and PSMC Logic C1ON C1SP C1VN C1OUT C1 C1VP C1POL To Interrupt and C2ON PSMC Logic C2SP C2OUT C2 C2POL Q D From TMR1 Q Clock Preliminary C1OE RB6/C1/PSMC1A C2SYNC C2OE 0 RB7/C2/PSMC1B/T1G 1 2001 Microchip Technology Inc. ...

Page 93

... C1VN of C1 connects to AN6 11 = C1VN of C1 connects to AN7 Note 1: C1OUT will only drive RB6/C1/PSMC1A if: (C2OE = 1) & (C2ON = 1) & (TRISB<7> & ((SMCON = 0) or ((SMCOM = 0) & (SCEN = 0))). Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. R-0 R/W-0 R/W-0 R/W-0 C1OE C1POL C1SP ...

Page 94

... Table 12-3. C2SP (CM2CON0<3>) configures the speed of the comparator. When C2SP is set, the comparator oper- ates at its normal speed. Clearing C2SP operates the 2 REF comparator in low power mode. Preliminary 2001 Microchip Technology Inc. ...

Page 95

... C2VN of C2 connects to AN6 11 = C2VN of C2 connects to AN7 Note 1: C2OUT will only drive RB7/C2/PSMC1B/T1G if: (C2OE = 1) & (C2ON = 1) & (TRISB<7> & ((SMCON = 0) or ((SMCOM = 0) & (SCEN = 0))). Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. PIC16C781/782 R/W-0 R/W-0 R/W-0 C2OE C2POL C2SP ...

Page 96

... U-0 U-0 U-0 U-0 — — — — Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary U-0 R/W-0 — C2SYNC bit Bit is unknown 2001 Microchip Technology Inc. ...

Page 97

... B’10001010’ ; Set C2; no out MOVWF CM2CON0 ; VREF2, AN6 BSF CM2CON1,C2SYNC ; CLK sync 2001 Microchip Technology Inc. PIC16C781/782 12.2.1 EXAMPLE: C2 SYNCHRONIZED TO T1CKI In this example, Comparator C2 is configured as a nor- mal voltage comparator synchronized to the T1CKI input. A block diagram of the comparator with external connections is shown in Figure 12-2 ...

Page 98

... Programmed for slow speed operation In addition, the output of comparator C2 must be inverted for common polarity with C1. A block diagram of the window comparator with exter- nal connections is shown in Figure 12-4. PIC16C78X - Preliminary C1OUT PSMC REF CM2CON1<6> CLPOL=1 CM2CON1<7> CLPOL=0 2001 Microchip Technology Inc. ...

Page 99

... USER_ISR BANKSEL CM2CON0 ; Select Bank 2 MOVF CM2CON0,F ; Clear C2 mismatch BANKSEL PIR1 ; Select Bank 0 BCF PIR1,C1IF ; Clear C2 int USER_ISR ;*** USER INTERRUPT ROUTING ;* SWAPF STATUS_SAVE,W; Restore W & ; STATUS MOVWF STATUS SWAPF W_SAVE,F SWAPF W_SAVE,W RETFIE ; Return 2001 Microchip Technology Inc. PIC16C781/782 Preliminary DS41171A-page 97 ...

Page 100

... C2CH0 0000 0000 0000 0000 C2SYNC 00-- ---0 00-- ---0 1111 1111 1111 1111 1111 1111 1111 1111 RA0 xxxx 0000 uuuu 0000 RB0 xxxx 0000 uuuu 0000 AN0 1111 1111 1111 1111 TMR1ON 0000 ---0 0000 ---0 TMR1IE 0000 ---0 0000 ---0 2001 Microchip Technology Inc. ...

Page 101

... C1POL C1 C2POL C2 Comparator Module 2001 Microchip Technology Inc. All pulse start and duty cycle limit timing features of the PSMC are derived from the internal CPU clock. Block diagrams for the PSMC are shown in Figure 13-1 through Figure 13-3. 13.1 Pulse Width Modulation (PWM) ...

Page 102

... DC = Duty Cycle 4 S1APOL New S Cycle A Set Dominant New R Cycle B Max DC S1BPOL C1OUT S Set SMCCS Dominant R C2OUT MINDC<1:0> C1OUT non-zero x non-zero Inactive 1 = Active H = High Preliminary Min DC Min DC Period SMCCS=0 PWM/PSM=1 SMCON=1 SMCOM=1 RB6/C1/PSMC1A Q RB7/C2/PSMC1B/T1G Q PSMC1A Output Signal Low 2001 Microchip Technology Inc. ...

Page 103

... PSMC1A OUTPUT SEQUENCE IN PWM MODE USING C1 AND C2 COMPARATORS Time MINDC<1:0> Beginning of PWM cycle During Min Duty Cycle After Min Duty Cycle, Before Max Duty Cycle Max Duty Cycle Legend Don’t Care q = Prior State 2001 Microchip Technology Inc. C1OUT C2OUT non-zero x non-zero ...

Page 104

... PSMC1B/T1G ASSUMES S1APOL=0 SMCCS Duty Cycle 4 S1APOL New S Cycle Set Dominant Max Switch C1OUT SMCCS SCEN C2OUT C1OUT PSMC1A Output Signal Active H = High L = Low Preliminary Period 15/16 Period HIGH IMPEDANCE SCEN=1 PWM/PSM=0 SMCON=1 SMCOM=0 RB6/C1/PSMC1A RB7/C2/PSMC1B/T1G Change 2001 Microchip Technology Inc. ...

Page 105

... The maximum duty cycle for either output is 50%. FIGURE 13-4: SLOPE COMPENSATION (SC) SWITCH OPERATION PWM Signal on PSMC1A pin DC = duty cycle T = Period SC Switch on PSMC1B pin Voltage across C 2001 Microchip Technology Inc. C1OUT C2OUT ...

Page 106

... Note: PSMC outputs must have their corre- <1:0> bits sponding direction bits cleared in TRISB; TRISB<6>: for PSMC1A, and TRISB<7> for PSMC1B. PSMC SMCOM SCEN Preliminary mode, the MAXDC <1:0> bits mode, the DC<1:0> bits PORTB TRISB<6> TRISB<7> 2001 Microchip Technology Inc. ...

Page 107

... Max duty cycle of 15/16 bit 1-0 DC<1:0>: Duty Cycle Select bits for PSM Mode 00 = Duty cycle of 1 Duty cycle of 3 Duty cycle of 5 Duty cycle of 15/16 Legend Readable bit - n = Value at POR 2001 Microchip Technology Inc. PIC16C781/782 R/W-0 R/W-0 R/W-0 R/W-0 MINDC1 MINDC0 MAXDC1 MAXDC0 ...

Page 108

... R = Readable bit - n = Value at POR DS41171A-page 106 R/W-0 U-0 R/W-0 R/W-0 S1BPOL — SCEN SMCOM W = Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared Preliminary R/W-0 R/W-0 PWM/PSM SMCCS bit Bit is unknown 2001 Microchip Technology Inc. ...

Page 109

... Diode D1 • C MAIN • OPAMP feedback filter • DAC reference 2001 Microchip Technology Inc. PIC16C781/782 The inner current loop is a pulsed current source driven by the PSMC. During the active phase of the output pulse, the inner loop builds up a current flow in inductor L1 ...

Page 110

... The OPAMP, Comparator and DAC must be configured, prior to enabling the PSMC to prevent unpredictable operation which may stress the power MOSFET transistors. DS41171A-page 108 +DCRAW MOSFET DRIVER RB6/C1/PSMC1A CURRENT TRANSFORMER RB7/C2/PSMC1B RB3/AN7/OPA RA1/AN1/OPA- RA4/AN0/OPA+ RA3/AN3/V 1 REF RB2/AN6 RB1/AN5/V DAC Preliminary LOAD C MAIN 2001 Microchip Technology Inc. ...

Page 111

... B’00001000’ MOVWF PSMCCON0 MOVLW B’00001010’ MOVWF PSMCCON1 BSF PSMCCON1,SMCON 2001 Microchip Technology Inc. PIC16C781/782 ; Select Bank 1 ; Set RA0,1,& inputs ; Set RB1,2,3,6 & inputs ; Configure RA0, RA1, RA3, ; RB1, RB2, RB3 as analog ; Select Bank 2 ; Set DAC to safe value ; Enable DAC, output ...

Page 112

... PSMC1B outputs are held tri-state until the PSMC is configured. Driver circuitry for all power MOSFET transistors must have a resistor bias to turn off the transistor in the event of tri-state conditions on either out- put to prevent undo stress on the MOS- FET's and their associated circuitry. Preliminary 2001 Microchip Technology Inc. ...

Page 113

... MOVLW B’0000000’ MOVWF PSMCCON0 MOVLW B’00000110’ MOVWF PSMCCON1 BSF PSMCCON1,SMCON 2001 Microchip Technology Inc. PIC16C781/782 ; Select Bank 1 ; Set RA0,1,& inputs ; Set RB1,2,3,6 & inputs ; Set AN0,1,3,5,6 & analog ; Select Bank 2 ; Set DAC to safe value ; Enable DAC, output ; and set DACREF = VDD ...

Page 114

... Data Sheet. Therefore, the designer should consult a text dealing with the design of motor speed controls and feedback control system, in general, for the necessary design guidance. Preliminary CURRENT TRANSFORMER MAIN D4 L2 LOAD 2001 Microchip Technology Inc. ...

Page 115

... MOVLW B’11001100’ MOVWF PSMCCON0 MOVLW B’00000010’ MOVWF PSMCCON1 BSF PSMCCON1,SMCON 2001 Microchip Technology Inc. PIC16C781/782 ; Select Bank 1 ; Set RA0,1 & inputs ; Set RB2 & inputs ; Set AN0,1,6,& analog ; Enable VR ; Select Bank 2 ; Set DAC to safe value ; Enable DAC, no output ...

Page 116

... FIGURE 13-7: EXAMPLE BRUSHLESS D.C. MOTOR CONTROL PIC16C781/782 F OSC / OPA V REF FIRMWARE FEEDBACK DAC CONTROL TIMER 1 DS41171A-page 114 H-BRIDGE DRIVER RB6/C1/PSMC1A ENABLE PHASE RB2/AN6 RB3/AN7/OPA RA0/AN0/OPA+ RA1/AN1/OPA- RA6/OSC2/CLKOUT/T1CKI Preliminary V MOTOR BRUSHLESS D.C. MOTOR HALL EFFECT SENSOR R SENSE 2001 Microchip Technology Inc. ...

Page 117

... PSMCCON0 SMCCL1 SMCCL0 MINDC1 MINDC0 MAXDC1 MAXDC0 112h PSMCCON1 SMCON S1APOL S1BPOL Legend unknown unchanged unimplemented, read as '0'. Shaded cells are not used for PSMC. 2001 Microchip Technology Inc. PIC16C781/782 Placing the PIC16C781/782 into SLEEP mode will stop the main oscillator for the microcontroller. The PSMC derives its timing from the main oscillator ...

Page 118

... PIC16C781/782 NOTES: DS41171A-page 116 Preliminary 2001 Microchip Technology Inc. ...

Page 119

... External RESET • Watchdog Timer Wake-up • Interrupt Additional information on special features is available in the PICmicro™ Mid-Range Reference Manual, (DS33023). 2001 Microchip Technology Inc. PIC16C781/782 14.1 Configuration Bits The configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations ...

Page 120

... Note 1: All of the CP bits must be given the same value to enable code protection. DS41171A-page 118 CP — BODEN MCLRE PWRTE WDTE (1) (1) (1) Crystal/Resonator Crystal/Resonator Crystal/Resonator Digital I/O Digital I/O CLKOUT Digital I/O CLKOUT Preliminary F0SC2 F0SC1 F0SC0 bit0 DD RA7/OSC1/CLKIN Crystal/Resonator Crystal/Resonator Crystal/Resonator CLKIN Digital I/O Digital I 2001 Microchip Technology Inc. ...

Page 121

... Rs (1) C2 Note 1: See Table 14-1 and Table 14-2 for recom- mended values of C1 and C2 series resistor (RS) may be required for AT strip cut crystals varies with the crystal chosen. 2001 Microchip Technology Inc. TABLE 14-1: Mode XT 455 kHz 2.0 MHz 4.0 MHz HS 8.0 MHz 16 ...

Page 122

... In the INTRC and RC modes, if the CLKOUT output is enabled, CLKOUT is held low during RESET. Preliminary RC OSCILLATOR MODE PIC16C781/782 RA7/OSC1/ Internal CLKIN Clock RA6/OSC2/CLKOUT/I1CKI = 5V and 25°C. See DD The nominal 2001 Microchip Technology Inc. ...

Page 123

... Ripple Counter PWRT Dedicated 10-bit Ripple Counter Oscillator 2001 Microchip Technology Inc. PIC16C781/782 Some registers are not affected in any RESET condi- tion. Their status is unknown on a Power-up Reset and unchanged in any other RESET. Most other registers are placed into an initialized state upon RESET. How- ...

Page 124

... PICmicro microcontroller operating in parallel. Table 14-5 shows the RESET conditions for some spe- cial function registers. Preliminary time-out PWRT falls below the trip point DD . The Power-up Timer BOR drops below V while the BOR , the Power-up BOR time delay. 2001 Microchip Technology Inc. ...

Page 125

... PWRTE = 0 XT, HS PWRT EC, RC, INTRC T 2001 Microchip Technology Inc. Clearing the OSCF (PCON<3>) enables oscillation at 37kHz, setting OSCF returns the oscillator to operation at 4MHz. The Watchdog Timer is a free running, on-chip dedi- cated oscillator and timer, which does not require any external components to operate. The WDT provides a system RESET in the event that software does not exe- cute a CLRWDT instruction within a specified interval ...

Page 126

... U-0 R/W-q R/W-1 — — WDTON OSCF W = Writable bit U = Unimplemented bit, read as ‘0’ ’1’ = Bit is set ’0’ = Bit is cleared ’q’ = Value depends on condition Bit Significance Preliminary U-0 R/W-q R/W-x — POR BOR bit 0 2001 Microchip Technology Inc. ...

Page 127

... PWRT TIME-OUT OST TIME-OUT INTERNAL RESET FIGURE 14-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED MCLR INTERNAL POR PWRT TIME-OUT OST TIME-OUT INTERNAL RESET 2001 Microchip Technology Inc. PIC16C781/782 Program STATUS Counter Register 000h 0001 1xxx 000h 000u uuuu 000h 0001 0uuu ...

Page 128

... Microchip Technology Inc. ...

Page 129

... PWRT TIME-OUT OST TIME-OUT INTERNAL RESET FIGURE 14-9: SLOW V RISE TIME (MCLR TIED MCLR INTERNAL POR PWRT TIME-OUT OST TIME-OUT INTERNAL RESET Note 1: This time depends on the oscillator circuit used. 2001 Microchip Technology Inc. PIC16C781/782 T PWRT T OST ) PWRT (1) T OST Preliminary ...

Page 130

... GIE decides whether or not the pro- cessor branches to the interrupt vector following a wake-up sequence. See Section 14.12 for details on SLEEP mode. Wake-up (If in SLEEP mode) T0IF T0IE INTF INTE RBIF RBIE PEIF PEIE GIE Preliminary pin is edge trig- R Interrupt to CPU 2001 Microchip Technology Inc. ...

Page 131

... Restores W. Note: The W_TEMP, STATUS_TEMP PCLATH_TEMP are defined in the com- mon RAM area (70h - 7Fh) to avoid regis- ter bank switching during context save and restore. 2001 Microchip Technology Inc. PIC16C781/782 EXAMPLE 14-1: SAVING STATUS, W, AND PCLATH REGISTERS #define W_TEMP #define STATUS_TEMP ...

Page 132

... MUX WDT Time-out Bit 6 Bit 5 Bit 4 Bit 3 BODEN MCLRE PWRTE WDTE INTEDG T0CS T0SE PSA — — WDTON OCSF Preliminary (1) PS<2:0> To TMR0 (Figure 5-2) (1) PSA Bit 2 Bit 1 Bit 0 FOSC2 FOSC1 FOSC0 PS2 PS1 PS0 — BOR POR 2001 Microchip Technology Inc. ...

Page 133

... Programmable low voltage detect. 4. Comparator interrupt-on-change. 5. OPA in Comparator mode using IOCB. 2001 Microchip Technology Inc. Other peripherals cannot generate interrupts since dur- ing SLEEP, no on-chip clocks are present. When the SLEEP instruction is being executed, the next instruction ( pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled) ...

Page 134

... GIE = ’1’ assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = ’0’, execution will continue in-line. 3: CLKOUT is not available in these osc modes, but shown here for timing reference. DS41171A-page 132 (1) T OST Processor in SLEEP PC+2 PC Inst( Inst( Dummy cycle Preliminary (2) Interrupt Latency 0004h 0005h Inst(0004h) Inst(0005h) Dummy cycle Inst(0004h) 2001 Microchip Technology Inc. ...

Page 135

... Byte-oriented operations • Bit-oriented operations • Literal and control operations 2001 Microchip Technology Inc. PIC16C781/782 All instructions are executed within one single instruc- tion cycle, unless a conditional test is true or the pro- gram counter is changed as a result of an instruction. ...

Page 136

... TO,PD 0000 0110 0100 1kkk kkkk kkkk Z 1000 kkkk kkkk 00xx kkkk kkkk 0000 0000 1001 01xx kkkk kkkk 0000 0000 1000 TO,PD 0000 0110 0011 C,DC,Z 110x kkkk kkkk Z 1010 kkkk kkkk 2001 Microchip Technology Inc. ...

Page 137

... Operation: (W) .AND. (k) (W) Status Affected: Z Description: The contents of W register are AND’ed with the eight bit literal 'k'. The result is placed in the W register. 2001 Microchip Technology Inc. PIC16C781/782 ANDWF AND W with f Syntax: [label] ANDWF Operands Operation: (W) .AND. (f) Status Affected: ...

Page 138

... W. If ’d’ the result is stored back in register ’f’. Decrement f [label] DECF f 127 d [0,1] ( (destination) Z Decrement register ’f’. If ’d’ the result is stored in the W regis- ter. If ’d’ the result is stored back in register ’f’. 2001 Microchip Technology Inc. ...

Page 139

... Status Affected: Z Description: The contents of register ’f’ are incremented. If ’d’ the result is placed in the W register. If ’d’ the result is placed back in reg- ister ’f’. 2001 Microchip Technology Inc. PIC16C781/782 INCFSZ Increment f, Skip if 0 Syntax: [ label ] Operands [0,1] ...

Page 140

... This is a two-cycle instruction. Rotate Left f through Carry [ label ] RLF f 127 d [0,1] See description below C The contents of register 'f' are rotated one bit to the left through the Carry Flag the result is placed in the W register the result is stored back in register 'f'. C Register f 2001 Microchip Technology Inc. ...

Page 141

... SUBLW k Operands 255 Operation (W) W) Status Affected: C, DC, Z Description: The W register is subtracted (2’s complement method) from the eight-bit literal 'k'. The result is placed in the W register. 2001 Microchip Technology Inc. PIC16C781/782 SUBWF Subtract W from f Syntax: [ label ] Operands 127 d [0,1] Operation: (f) - (W) Status Affected: C, DC, Z Description: Subtract (2’ ...

Page 142

... Operation: (W) .XOR. (f) destination) Status Affected: Z Description: Exclusive OR the contents of the W register with register ’f’. If ’d’ the result is stored in the W register. If ’d’ the result is stored back in register ’f’. DS41171A-page 140 f,d Preliminary 2001 Microchip Technology Inc. ...

Page 143

... A project manager • Customizable toolbar and key mapping • A status bar • On-line help 2001 Microchip Technology Inc. PIC16C781/782 The MPLAB IDE allows you to: • Edit your source files (either assembly or ‘C’) • One touch assemble (or compile) and download ...

Page 144

... ICEPIC In-Circuit Emulator The ICEPIC low cost, in-circuit emulator is a solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X and PIC16CXXX families of 8-bit One- Time-Programmable (OTP) microcontrollers. The mod- ular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of inter- changeable personality modules, or daughter boards ...

Page 145

... PIC16C92X PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant. 2001 Microchip Technology Inc. 16.11 PICDEM 1 Low Cost PICmicro Demonstration Board The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip’s microcontrollers. The microcontrollers sup- ...

Page 146

... Programming Tools K L evaluation and programming tools support EE OQ Microchip’s HCS Secure Data Products. The HCS eval- uation kit includes a LCD display to show changing codes, a decoder to decode transmissions and a pro- gramming interface to program test transmitters. Preliminary 2001 Microchip Technology Inc. ...

Page 147

... PIC16C6X á á á á PIC16C5X á á á PIC14000 á á á á PIC12CXXX Tools Software Emulators 2001 Microchip Technology Inc. á á á á á á á á á á á á á á á á á á ...

Page 148

... PIC16C781/782 NOTES: DS41171A-page 146 Preliminary 2001 Microchip Technology Inc. ...

Page 149

... This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. 2001 Microchip Technology Inc. (except V , MCLR and RA4) ................................... -0. pins............................................................................................... ± ...

Page 150

... Note 1: The shaded region indicates the permissible combinations of voltage and frequency. FIGURE 17-2: PIC16LC781/782 VOLTAGE-FREQUENCY GRAPH, -40 C 5.5 4.5- 4 (Volts) 2.7 0 Note 1: The shaded region indicates the permissible combinations of voltage and frequency. DS41171A-page 148 4 10 Frequency (MHz Frequency (MHz) Preliminary 2001 Microchip Technology Inc. ...

Page 151

... The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins configured as iputs and tied to V 2001 Microchip Technology Inc. Standard Operating Conditions (unless otherwise stated) Operating temperature-40°C Min Typ† ...

Page 152

... PIN SS µA Vss Pin at PIN DD hi-impedance nA Vss Pin at PIN DD hi-impedance µA Vss V V PIN DD µA Vss XT, HS, LP PIN DD and EC osc configuration 8 -3 RA4 pin pF In XT, HS and LP modes when external clock is used to drive OSC1. pF 2001 Microchip Technology Inc. ...

Page 153

... Fall H High I Invalid (Hi-impedance) L Low FIGURE 17-3: LOAD CONDITIONS Load condition Pin 464 for all pins except OSC2 15 pF for OSC2 output 2001 Microchip Technology Inc. T Time osc OSC1 t0 T0CKI t1 T1CKI P Period R Rise V Valid Z Hi-impedance High High Low Low Load condition 2 ...

Page 154

... Max Units Conditions 75 200 ns (Note 1) 75 200 ns (Note 1) 35 100 ns (Note 1) 35 100 ns (Note 1) — 0. (Note 1) CY — — ns (Note 1) — — ns (Note 1) 50 150 ns — — ns — — ns — — — — — — ns — — ns 2001 Microchip Technology Inc. ...

Page 155

... All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices. 2001 Microchip Technology Inc ...

Page 156

... Note 1: Refer to Figure 17-3 for load conditions. FIGURE 17-7: BROWN-OUT RESET TIMING V DD DS41171A-page 154 T +85 C (industrial) A range is described in Section 17-1. DD (1) Characteristic Min Typ 3.65 4.00 3.55* 4.00 Frequency Preliminary Max Units Conditions 4.28 MHz V = 5.0V DD 4.31* MHz 2001 Microchip Technology Inc. ...

Page 157

... Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. FIGURE 17-8: BROWN-OUT RESET CHARACTERISTICS (device in Brown-out Reset) RESET (due to BOR) Note 1: Only if Power-up Timer is enabled. If Timer is disabled, time-out 2001 Microchip Technology Inc. Min Typ† 2 — — 1024 T OSC ...

Page 158

... PIC16C781/782 FIGURE 17-9: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS RA4/T0CKI RA6/OSC2/CLKOUT/T1CKI TMR0 or TMR1 Note: Refer to Figure 17-3 for load conditions. DS41171A-page 156 Preliminary 48 2001 Microchip Technology Inc. ...

Page 159

... Tcke2tmrl Delay from external clock edge to timer increment * These parameters are characterized but not tested. † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. 2001 Microchip Technology Inc. PIC16C781/782 Min Typ† No Prescaler 0. — ...

Page 160

... GBWP = 1 following Auto Calibration connected < V < OUT connected 100 mV < V < 100 mV OUT DD GBWP = 0 following Auto Calibration connected < V < OUT 100 k connected < V < OUT DD GBWP = 1 Following Auto Calibration connected Following Auto Calibration V CALREF = 0 2001 Microchip Technology Inc. ...

Page 161

... Calibration Time Turn On Time Phase Margin Slew Rate Note: Data in ‘Typ’ column unless otherwise stated. These parameters are for design guidance only and are not tested. 2001 Microchip Technology Inc. Standard Operating Conditions (unless otherwise stated 2.7V to 5.5V GND ...

Page 162

... Input overdrive = 10 mV, step = 110 mV / 100 pF C1SP = 1, C2SP = 1, Comparator output is available on I/O pin, Input overdrive = 10 mV, step = 110 mV / 100 pF C1SP = 0, C2SP = 0, Comparator output is available on I/O pin, Input overdrive = 10 mV, step = 110 mV / C1SP = 0, C2SP = C1SP = 1, C2SP = 2001 Microchip Technology Inc. ...

Page 163

... Slew Rate Settling Time Turn On Time Note 1: Data in ‘Typ’ column is at 5V, 25° C unless otherwise stated. These parameters are for design guidance only and are not tested. 2001 Microchip Technology Inc. PIC16C781/782 Standard Operating Conditions (unless otherwise stated 2.7V to 5.5V 25° ...

Page 164

... Preliminary V = 1.32V BGAP (internal use only) Conditions s Defined as the time between the instant that the bandgap is enabled and the moment that the bandgap reference voltage is stable. T +85°C for industrial A Conditions V 3. SOURCE SINK 2001 Microchip Technology Inc. ...

Page 165

... Data in “Typ” column unless otherwise stated. These parameters are for design guidance only and are not tested. Note 1: Production tested 25°C. Specifications over temperature limits ensured by characterization. AMB 2001 Microchip Technology Inc. LVD (LVDIF can be cleared in software anytime during the gray area) Standard Operating Conditions (unless otherwise stated) Operating temperature -40° ...

Page 166

... LSb ADC = AV = 3.0V REF DD — ADC SS AIN REF V — V — k — A Average current consumption (1) when ADC is on. A During V acquisition. AIN Based on differential of V HOLD AIN To charge C , see HOLD Section 9.3. A During ADC Conversion cycle. and ADC . SS REF 2001 Microchip Technology Inc. ...

Page 167

... Data in “Typ” column unless otherwise stated. These parameters are for design guidance only and are not tested. § These specifications ensured by design. Note 1: ADRES register may be read on the following T 2: See Section 13.1 for min. conditions. 2001 Microchip Technology Inc. (1) 131 130 7 ...

Page 168

... PIC16C781/782 NOTES: DS41171A-page 166 Preliminary 2001 Microchip Technology Inc. ...

Page 169

... Max or Maximum represents the mean +3 over the temperature range of -40°C to 85°C. Min or Minimum represents the mean -3 over the tem- perature range of -40°C to 85°C. Graphs and Tables are not available at this time. 2001 Microchip Technology Inc. PIC16C781/782 DD Preliminary DS41171A-page 167 ...

Page 170

... PIC16C781/782 NOTES: DS41171A-page 168 Preliminary 2001 Microchip Technology Inc. ...

Page 171

... Standard PICmicro device marking consists of Microchip part number, year code, week code, and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price. 2001 Microchip Technology Inc. PIC16C781/782 Example PIC16C781 ...

Page 172

... Preliminary A2 MILLIMETERS MIN NOM MAX 20 0.65 1.73 1.85 1.98 1.63 1.73 1.83 0.05 0.15 0.25 7.59 7.85 8.18 5.11 5.25 5.38 7.06 7.20 7.34 0.56 0.75 0.94 0.10 0.18 0.25 0.00 101.60 203.20 0.25 0.32 0. 2001 Microchip Technology Inc. ...

Page 173

... CERDIP Windowed Diagram not available at this time. 2001 Microchip Technology Inc. PIC16C781/782 Preliminary DS41171A-page 171 ...

Page 174

... Preliminary A2 MILLIMETERS MIN NOM MAX 20 1.27 2.36 2.50 2.64 2.24 2.31 2.39 0.10 0.20 0.30 10.01 10.34 10.67 7.39 7.49 7.59 12.60 12.80 13.00 0.25 0.50 0.74 0.41 0.84 1. 0.23 0.28 0.33 0.36 0.42 0. 2001 Microchip Technology Inc. ...

Page 175

... Mold Draft Angle Top Mold Draft Angle Bottom * Controlling Parameter § Significant Characteristic Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010” (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-019 2001 Microchip Technology Inc Units INCHES* ...

Page 176

... PIC16C781/782 NOTES: DS41171A-page 174 Preliminary 2001 Microchip Technology Inc. ...

Page 177

... RB7/C2/PSMC1B/T1G Pin ......................................... 44 RC Oscillator Mode................................................... 120 Timer0 ......................................................................... 51 Timer0/WDT Prescaler................................................ 53 TIMER1....................................................................... 58 Watchdog Timer (WDT) ............................................ 130 Boost LC Switching Power Supply.................................... 107 2001 Microchip Technology Inc. PIC16C781/782 BOR DC Characteristics.................................................... 164 BOR. See Brown-out Reset Brown-out Reset (BOR).................................... 117, 125, 126 Buck Configuration LC Power Supply............................... 112 Buck LC Switching Power Supply ...

Page 178

... OPA Auto Calibration.......................................................... 83 OPA Module Associated Registers .................................................. 87 Common Mode Voltage Range................................... 86 Effects of a RESET ..................................................... 86 Gain Bandwidth Product ............................................. 86 Input Offset Voltage .................................................... 86 Leakage Current ......................................................... 86 Open Loop Gain ......................................................... 86 OPA Offset Voltage ............................................................ 84 OPCODE Field Descriptions............................................. 133 Operational Amplifier (OPA) Module .................................. 83 Preliminary 2001 Microchip Technology Inc. ...

Page 179

... RB2/AN6 ....................................................................... 8 RB3/AN7/OPA............................................................... 8 RB4 ............................................................................... 8 RB5 ............................................................................... 8 RB6/C1/PSMC1A.......................................................... 8 RB7/C2/PSMC1B/T1G.................................................. 9 V ............................................................................... ................................................................................ 9 SS Pinout Description PIC16C781/782 ............................................................ 8 2001 Microchip Technology Inc. PIC16C781/782 PIR1 Register ADIF Bit ...................................................................... 21 C1IF Bit....................................................................... 21 C2IF Bit....................................................................... 21 LVDIF Bit .................................................................... 21 TMR1IF Bit ................................................................. 21 PLVD DC Characteristics.................................................... 163 PLVD Example ................................................................... 67 PMCON1 ............................................................................ 47 PMDATH and PMDATL Registers...................................... 47 PMR Associated Register Summary ................................... 50 Pointer, FSR ...

Page 180

... PORTA Register ......................................................... 13 PORTB Register ................................................... 13, 15 PSMCCON0 Register ................................................. 15 PSMCCON1 Register ................................................. 15 REFCON Register ...................................................... 14 STATUS Register...................................... 13, 14, 15, 16 Summary .................................................................... 13 T1CON Register ......................................................... 13 TMR0 Register...................................................... 13, 15 TMR1H Register ......................................................... 13 TMR1L Register.......................................................... 13 TRISA Register........................................................... 14 TRISB Register..................................................... 14, 16 WPUB Register........................................................... 14 Stack................................................................................... 23 STATUS Register ............................................................. 129 Preliminary 2001 Microchip Technology Inc. ...

Page 181

... Timer0 and Timer1 External Clock............................ 156 Timer1 ....................................................................... 156 Wake-up from SLEEP via Interrupt ........................... 132 TRISA, ANSEL, and Control Precedence ........................... 26 TRISB, ANSEL, and Control Precedence ........................... 36 Typical Low Voltage Detect Application .............................. 63 2001 Microchip Technology Inc. PIC16C781/782 V Voltage Reference Module Effects of a RESET..................................................... 61 Voltage Reference Module (VR)......................................... Register ...

Page 182

... PIC16C781/782 NOTES: DS41171A-page 180 Preliminary 2001 Microchip Technology Inc. ...

Page 183

... Microchip Products • Conferences for products, Development Sys- tems, technical information and more • Listing of seminars and events 2001 Microchip Technology Inc. PIC16C781/782 Systems Information and Upgrade Hot Line The Systems Information and Upgrade Line provides system users a listing of the latest versions of all of Microchip’ ...

Page 184

... Is there any incorrect or misleading information (what and where)? 7. How would you improve this document? 8. How would you improve our software, systems, and silicon products? DS41171A-page182 Total Pages Sent FAX: (______) _________ - _________ N Literature Number: DS41171A Preliminary 2001 Microchip Technology Inc. ...

Page 185

... The Microchip Worldwide Site (www.microchip.com) Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using. New Customer Notification System Register on our web site (www.microchip.com/cn) to receive the most current information on our products. 2001 Microchip Technology Inc. PIC16C781/782 XXX Examples: ...

Page 186

... Korea Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882 Tel: 82-2-554-7200 Fax: 82-2-558-5934 Singapore Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980 Tel: 65-334-8870 Fax: 65-334-8850 Taiwan Microchip Technology Taiwan 11F-3, No. 207 ...