AT89LS52-16PC Atmel, AT89LS52-16PC Datasheet - Page 10

AT89LS52-16PC

Manufacturer Part Number

AT89LS52-16PC

Description

IC MCU 8K FLASH LV 16MHZ 40-DIP

Manufacturer

Atmel

Series

89LSr

Datasheet

1.AT89LS52-16JU.pdf

(39 pages)

Specifications of AT89LS52-16PC

Core Processor

8051

Core Size

8-Bit

Speed

16MHz

Connectivity

UART/USART

Peripherals

WDT

Number Of I /o

32

Program Memory Size

8KB (8K x 8)

Program Memory Type

FLASH

Ram Size

256 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 4 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

40-DIP (0.600", 15.24mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Data Converters

-

Table 5-4.

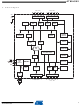

6. Memory Organization

6.1

6.2

10

AUXR1

–

DPS

Program Memory

Data Memory

AT89LS52

Reserved for future expansion

Data Pointer Register Select

DPS

0

1

AUXR1: Auxiliary Register 1

Address = A2H

Not Bit Addressable

Bit

Selects DPTR Registers DP0L, DP0H

Selects DPTR Registers DP1L, DP1H

MCS-51 devices have a separate address space for Program and Data Memory. Up to 64K

bytes each of external Program and Data Memory can be addressed.

If the EA pin is connected to GND, all program fetches are directed to external memory.

On the AT89LS52, if EA is connected to V

1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are

directed to external memory.

The AT89LS52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel

address space to the Special Function Registers. This means that the upper 128 bytes have the

same addresses as the SFR space but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the address mode used

in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR

space. Instructions which use direct addressing access of the SFR space.

For example, the following direct addressing instruction accesses the SFR at location 0A0H

(which is P2).

Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the

following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at

address 0A0H, rather than P2 (whose address is 0A0H).

Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data

RAM are available as stack space.

–

7

MOV 0A0H, #data

MOV @R0, #data

–

6

–

5

–

4

CC

–

3

, program fetches to addresses 0000H through

–

2

Reset Value = XXXXXXX0B

–

1

DPS

2601C–MICRO–06/08

0